I'm attempting to add support for a pseudo digital protocol to a project of mine. I'm attempting to implement the dShot protocol for controlling ESCs on my thrust stand, and having some issues. The TivaC doesn't appear to have very robust output control. You can see what I'm trying to do here:

Basically the protocol uses a modified PWM signal with each bit being 1.67us period with 1250ns representing a 1 and 635ns representing 0, basically encoding a 2048 bit throttle signal with some CRC data and a telemetry call bit crammed on the ends. After a couple days I've gotten to the point of using a PWM timer synced with a GP timer to attempt to modify the duty cycle for each bit, however I'm not having much luck. Is there a more precise way of accomplishing this? I'd like to not have to switch MCUs, but I know the ESP32 can do this easily with their RMT methodology and the STM chips can do with with a DMA transfer. I looked at the uDMA implementation in the TivaC and it doesn't appear to operate in a way that would work to toggle pins like this.

This is the output signal I'm getting on my relatively limited DSO Nano from the TivaC:

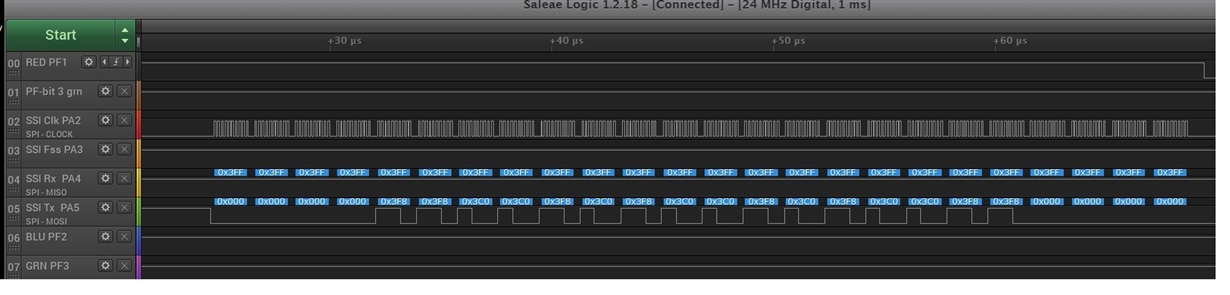

And this is the output signal as seen from an STM32F405 that is working properly:

Any help would be very much appreciated.