Part Number: TM4C129DNCPDT

We have a TIVA 129 configured with PLL frequency of 480MHz and system clock of 120 MHz. To reduce power at certain times, we wish to reduce the sysclk to a much lower value, while keeping everything else (including USB) operational. During these times we know the I/O and processor load will be greatly reduced.

Using USB on the TIVA as a CDC device.

The PLL remains at 480MHz, and we change SYSDIV and MEMTIM0 as indicated at the end of section 5.3 of the manual. This works as desired, and we see good power savings when changing from 120MHz to, for example, 30MHz, and everything is reliable.

We would like to go to a lower rate and save more power. When dropping to, for example, 12MHz, the USB becomes unreliable. (We are using the CDC device driver). When entering chars from a terminal emulator at human entry rates, some characters from the terminal emulator are either not received or not echoed (the echo is our code, which is reliable at all rates). Also, when a char is dropped, the processor seems to be stuck somewhere in the usb driver (from TI). The flashing LED indicates that the processor is still up and that interrupts continue to be serviced.

Disconnecting (logically, not physically) and reconnecting the terminal emulator often shows some of the "stuck" output and response, and also indicates that some of the input characters were missed at times. In this case, reconnecting shows the same device name under Linux, so we know that re-enumeration of devices on the bus has not occurred. (Using coolTerm under Linux).

The tivaware usb library readme file indicates revision 2.1.0.12573.

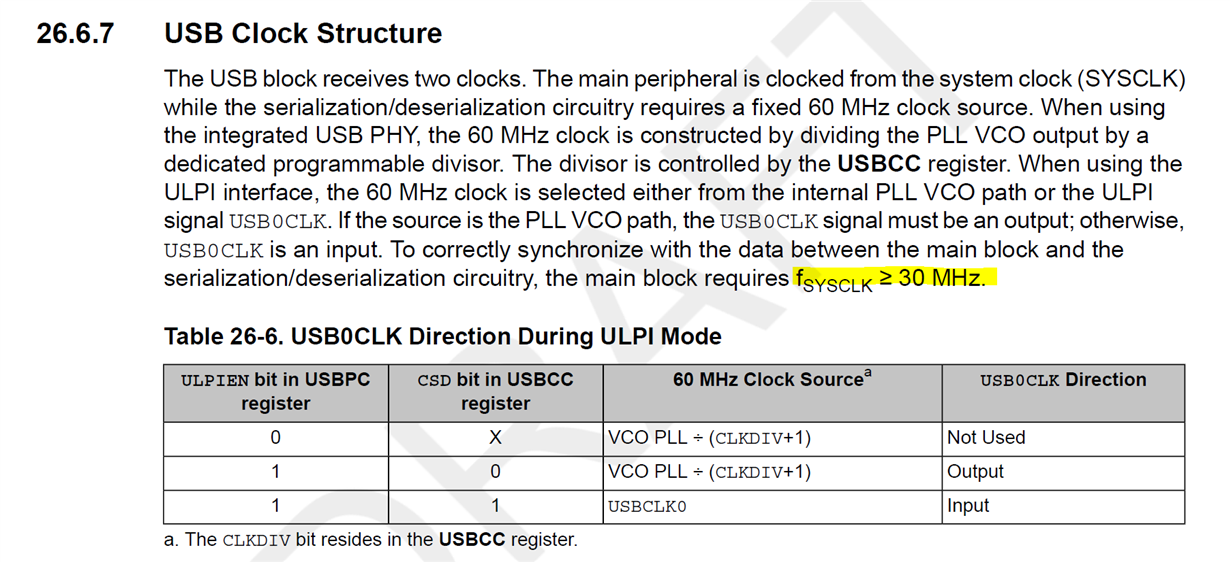

Looking for suggestions on this, or similar experience, or whether or not there a lower limit to sysclk when using USB. Again the PLL remains at 480, so the USB controller in the TIVA should be fine.

Thank you and regards,

Tim