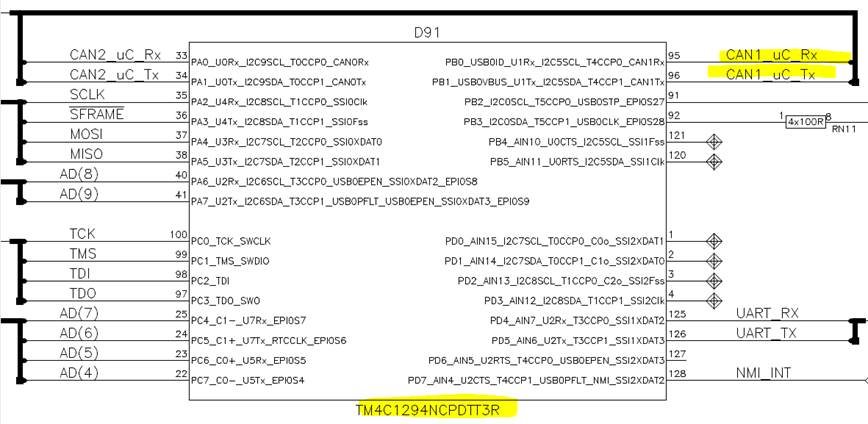

Part Number: TM4C1294NCPDT

Hi,

I am writing to you because of a question about the use of the TM4C1294NCPDTT3R or the point GPIO#09 in the Errata document (www.ti.com/.../spmz850g.pdf).

Unfortunately we are dependent on the two pins PB0 and PB1.

The first thought was to provide the output with a C-R-C network so that the edge steepness is always >> 2ns.

But we don't really trust this solution, because instead of this simple solution the Errata document recommends "Do not use PB0 and PB1" as workaround.

Can you please find out if a C-R-C network is a reliable solution?

Are there already implementations and experiences with other designs?

Thanks

Fred