Other Parts Discussed in Thread: TPD4E1B06, ESDS314

Tool/software: Code Composer Studio

I am having an issue with a custom board that we have developed using the TM4C1294NCPDT. I have used the chip before but have never used it for an Ethernet connection, I was able to get some proof of concept code working on the launchpad, and was then able to get it working OK on my custom board.

However later discovered an issue that didnt appear to show up at all when I was doing my initial development, sometimes when the board is powered on the ethernet link is either very slow to establish or never establishes.

I can generally get the link to connect by waiting 30 seconds to see if the link gets establish, if it doesn't I hit the hardware reset button and try again.

If the link is established, and then a connection to our other controller is established the link seems to be pretty reliable and hasn't dropped out even when left powered on overnight.

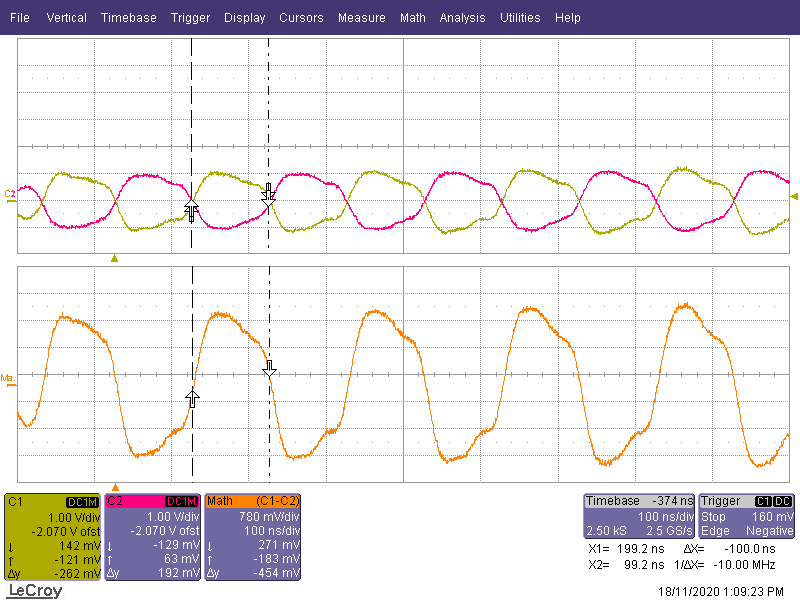

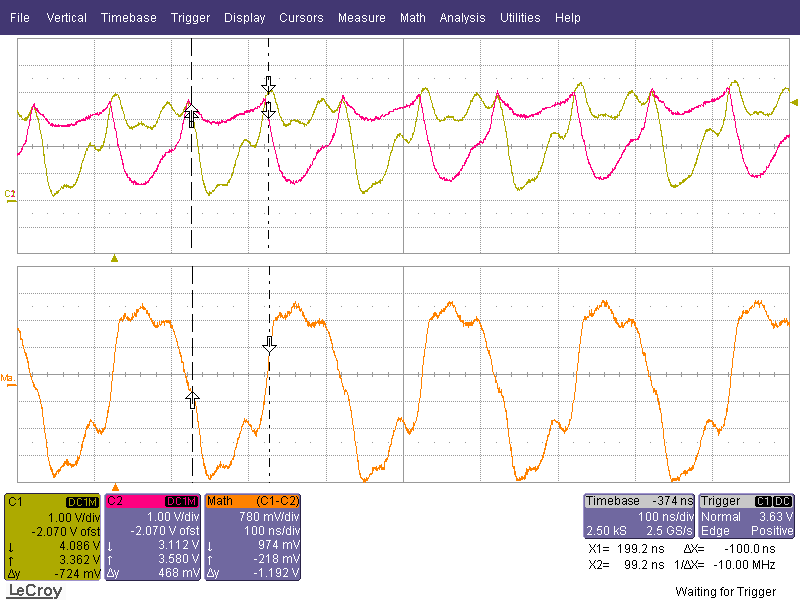

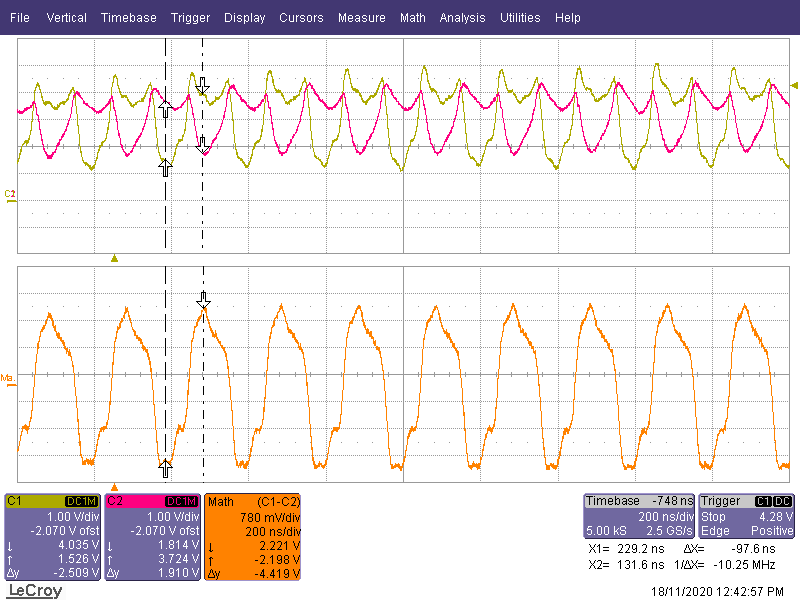

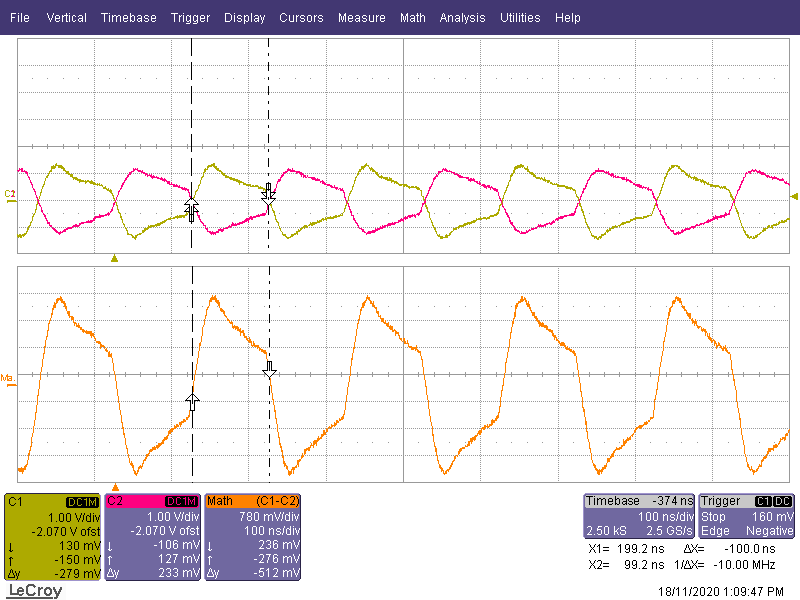

I have followed the TI guidelines on the Ethernet connection with the exception that the pairs are also used for power supply and some very slow digital signals, for the purposes of this testing none of these signals are switching and are held to one supply rail or the other. The result of this is that the signal path between the TM4C and the industrial controller effectively has 3 sets of magnetics instead of the usual two. One on the board with the TM4C as per TI recommendations, one in the middle where power and signals are injected, and one in the industrial controller. I am aware the extra set of magnetics is introducing losses into the system however the cable run is pretty short (<5m), it is my understanding that this is more or less how some of the cheap passive POE injectors work.

Our application comms is pretty simple, we are initializing LWIP with a static IP address, waiting for a link and then establishing a TCP connection with our remote device. I have tried the suggestion of turning of the flash prefetch with no effect.

I have done my best to tease some additional information out of LWIP on where I might be going wrong without much success, and have not done anything on the hardware side of things beyond switching out and testing different cables. I haven't bothered probing the signals as I am not sure what I would be looking for anyway.

If anybody has recommendations on where I should be poking around in software or hardware to try and diagnose the issue I would be very thankful.

I have included the relevant section of schematic for our mainboard, as well as the schematic for the injector board.