Hi:

I met some question in my code debug ,Below is My source code

#include "all_header.h"

static uint32_t Received_ID ;

g_dmaCTRL g_dmaCTRLPKT; /*dma control packet configuration stack*/

#define D_COUNT 8

#define D_SIZE 8

int data;

uint32 DMA_Comp_Flag;

uint32 cnt = 0;

uint32 error = 0;

uint32 tx_done = 0;

uint32 CpuCount = 0;

uint32 timer0 = 0;

uint8_t tx_data1[D_COUNT] = {1, 2, 3, 4, 4, 3, 2, 1}; /*transmit buffer in sys ram*/

uint8_t tx_data2[D_COUNT] = {1, 3, 5, 7, 9, 11, 13, 15};

uint8_t tx_data3[D_COUNT] = {2, 4, 6, 8, 10, 12, 14, 16};

uint8_t rx_data[D_COUNT] = {0}; /*receive buffer in sys ram*/

void delay(uint32 time);

void dmaConfigCtrlRxPacket(uint32 sadd,uint32 dadd,uint32 dsize);

void dmaGroupANotification(dmaInterrupt_t inttype, uint32 channel)

{

DMA_Comp_Flag = 0x5555AAAA;

}

void main(void)

{

_enable_interrupt_(); /*enable irq interrupt in Cortex R4*/

DMA_Comp_Flag = 0xAAAA5555; /* Reset the Flag */

rtiInit(); /*Initialize RTI driver*/

rtiEnableNotification(rtiNOTIFICATION_COMPARE0); /*Enable RTI compare 0 interrupt notification*/

_enable_IRQ();

rtiStartCounter(rtiCOUNTER_BLOCK0); /*Start RTI Counter Block 0*/

u8gv_tmr_addr = get_tmr_addr();

canInit(); /* initialize can*/

vimInit();

canREG1->CTL |= (uint32)(1<<20); /*Enable DE3 bit in CTL register to trigger DMA when IF3 receives data*/

canREG1->IF3OBS = 0x0000001AU; /* Read ARB, DATA A & B - 8 bytes */

canREG1->IF3UEy[0] = 0xFFFFFFFFU; /*Message box of RX 2,4,6 configured for auto update*/

/* - DMA Configuration */

dmaEnable(); /* Enable DMA */

dmaEnableInterrupt(DMA_CH0, FTC); /* Enable Interrupt after reception of data */

dmaReqAssign(DMA_CH0,16U); /*assigning dma request: channel-0 with request line - 16 ( DCAN1IF3)*/

vimEnableInterrupt((uint32)33U,SYS_IRQ); /* VIM DMA FTCA:Frame transfer complete*/

dmaConfigCtrlRxPacket((uint32)(&(canREG1->IF3DATx[0])),(uint32)(&rx_data),1);

dmaSetCtrlPacket(DMA_CH0, g_dmaCTRLPKT); /*setting dma control packets for transmit*/

dmaREG->GCHIENAS |= 1<<DMA_CH0; /* enable the channel global interrupt */

while(1)

{

DMA_Comp_Flag = 0xAAAA5555; /* Reset the Flag */

canTransmit(canREG1, canMESSAGE_BOX3, (const uint8 *)&tx_data2[0]); /* transmit on can1 */

while(DMA_Comp_Flag != 0x5555AAAA); /* Wait for the DMA interrupt ISR to set the Flag */

}

return 0;

}

void canMessageNotification(canBASE_t *node, uint32_t messageBox)

{

while(!canIsRxMessageArrived(canREG1, canMESSAGE_BOX4))

;

canGetData(canREG1, canMESSAGE_BOX4, (uint8 *)&rx_data[0]);

Received_ID = (canREG1->IF3ARB & 0x1FFC0000)>>18;

printf("rx_data : %x %x %x %x %x %x %x %x \n", rx_data[0],rx_data[1],rx_data[2],rx_data[3],rx_data[4],rx_data[5],rx_data[6],rx_data[7]);

printf("Received_ID : %x\n", Received_ID);

/* - setting the dma channel to trigger on S/w request */

dmaSetChEnable(DMA_CH0, DMA_SW);

}

void dmaConfigCtrlRxPacket(uint32 sadd,uint32 dadd,uint32 dsize)

{

g_dmaCTRLPKT.SADD = sadd; /* source address */

g_dmaCTRLPKT.DADD = dadd; /* destination address */

g_dmaCTRLPKT.CHCTRL = 0; /* channel control */

g_dmaCTRLPKT.FRCNT = 1; /* frame count */

g_dmaCTRLPKT.ELCNT = dsize; /* element count */

g_dmaCTRLPKT.ELDOFFSET = 0; /* element destination offset */

g_dmaCTRLPKT.ELSOFFSET = 0; /* element source offset */

g_dmaCTRLPKT.FRDOFFSET = 0; /* frame destination offset */

g_dmaCTRLPKT.FRSOFFSET = 0; /* frame source offset */

g_dmaCTRLPKT.PORTASGN = 4; /* port b */

g_dmaCTRLPKT.RDSIZE = ACCESS_64_BIT; /* read size */

g_dmaCTRLPKT.WRSIZE = ACCESS_64_BIT; /* write size */

g_dmaCTRLPKT.TTYPE = FRAME_TRANSFER ; /* transfer type 一个请求触发一帧传输 */

g_dmaCTRLPKT.ADDMODERD = ADDR_FIXED; /* address mode read */

g_dmaCTRLPKT.ADDMODEWR = ADDR_FIXED; /* address mode write */

g_dmaCTRLPKT.AUTOINIT = AUTOINIT_ON; /* autoinit */

}

/* USER CODE END */

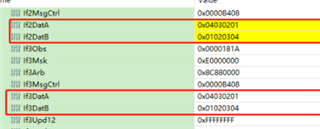

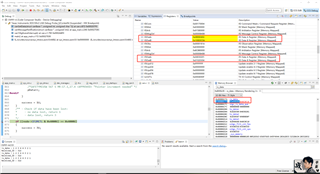

The main question is: When the data collected in my IF2 has been updated, why the data monitored by the corresponding IF3 has not been synchronized and changed?