Part Number: RM48L730

Hello.

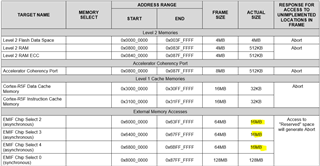

1. Whether the EMIF(External Memory Interface) in RM48L730 can connect to NAND Flash?

2. Whether there is a memory size limitation for this NAND FLash? My target flash size is 512Mbytes or 1Gbytes.

3. The ECC described in the datasheet is for On-chip Flash or external NAND FLash? The ECC for external NAND Flash is hardware ECC or software ECC? How many bits Error Detection and Error Correction it supported?

Thank you.