Hi Wang, As per your earlier recommendation we used DMB instructions before the application reads the DMA buffers every time. But we are still seeing the cache and the RAM are not coherent and observing data misses.

We are clueless on what we are supposed to do. But when the shared RAM region is cache disabled, the issue is not observed. But, running in cache disabled mode may impact the timing, so we were thinking, what exactly we need to do to resolve this problem.

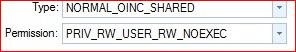

When cache is disabled, we used below configuration.

Thanks,

Kishore