- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

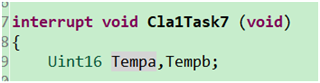

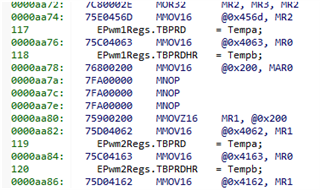

no our project use 280049's CLA, The code was ported from 28035. (both project's opt level is 0--register optimizations)

in 28035 CLA code i use two temporary variables: Uint16 Tempa,Tempb; and the code is

you can see the Tempa and Tempb's value is gived to MR0 and MR1, and when use Tempa and Tempb, the instruction is very sample, this save more time

that's work well.

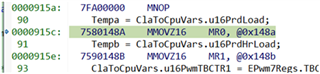

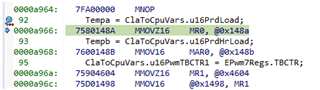

but in 280049, the Tempa and Tempb's value is gived to MR0 and MAR0

this load to when i use Tempb, MAR0 must first give to 0x200, and then 0x200's value give to TBPRDHR

why this? can CLA use the stack's space? How to set or optimize to obtain the concise instructions like 28035's CLA when use 280049's CLA, How can i use temporary variables?

Hi,

Can you let me know the compiler version used for both the projects?

Thanks,

Ashwini

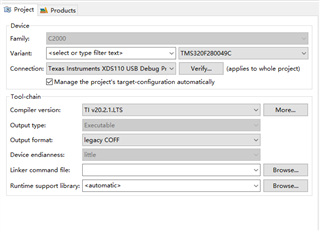

28035 project: TI v6.4.2 use opt=0

280049c project:TI v20.2.1.LTS use opt =0

Hi,

Thanks for the information.

I am sorry for the delay in reply. I was out of office last week and hence was not able to reply sooner.

I will sync up with the experts and let you know.

Thanks,

Ashwini

Hi,

Please could you submit a test case so the team can do deeper analysis. Here are the steps: How to Submit a Compiler Test Case.

Thanks,

Ashwini

sorry, for my company's security stratege i can not sent the whole code for you, but I can copy some key pieces below: (in cla file)

interrupt void Cla1Task7 (void)

{

Uint16 Tempa,Tempb;

.........................here is code cal ClaToCpuVars.u16PrdLoad and ClaToCpuVars.u16PrdHrLoad.................................

Tempa = ClaToCpuVars.u16PrdLoad;

Tempb = ClaToCpuVars.u16PrdHrLoad;

ClaToCpuVars.u16PwmTBCTR1 = EPwm7Regs.TBCTR;

//running time get = 181cnt

/*************************************************************************/

// load CMPA and CMPAHR

/*************************************************************************/

EPwm1Regs.CMPA.bit.CMPA = ClaToCpuVars.u16Pwm1Cmpa;

EPwm1Regs.CMPB.bit.CMPB = ClaToCpuVars.u16Pwm1Cmpb;

EPwm2Regs.CMPA.bit.CMPA = ClaToCpuVars.u16Pwm2Cmpa;

EPwm2Regs.CMPB.bit.CMPB = ClaToCpuVars.u16Pwm2Cmpb;

EPwm3Regs.CMPA.bit.CMPA = ClaToCpuVars.u16Pwm3Cmpa;

EPwm3Regs.CMPB.bit.CMPB = ClaToCpuVars.u16Pwm3Cmpb;

EPwm4Regs.CMPA.bit.CMPA = ClaToCpuVars.u16Pwm4Cmpa;

EPwm4Regs.CMPB.bit.CMPB = ClaToCpuVars.u16Pwm4Cmpb;

EPwm5Regs.CMPA.bit.CMPA = ClaToCpuVars.u16Pwm5Cmpa;

EPwm5Regs.CMPB.bit.CMPB = ClaToCpuVars.u16Pwm5Cmpb;

EPwm6Regs.CMPA.bit.CMPA = ClaToCpuVars.u16Pwm6Cmpa;

EPwm6Regs.CMPB.bit.CMPB = ClaToCpuVars.u16Pwm6Cmpb;

/*************************************************************************/

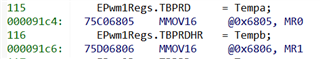

// load TBPRD and TBPRDHR

/*************************************************************************/

// EPwm1Regs.TBPRD = Tempa;

// EPwm1Regs.TBPRDHR = Tempb;

EPwm2Regs.TBPRD = Tempa;

EPwm2Regs.TBPRDHR = Tempb;

EPwm3Regs.TBPRD = Tempa;

EPwm3Regs.TBPRDHR = Tempb;

EPwm4Regs.TBPRD = Tempa;

EPwm4Regs.TBPRDHR = Tempb;

EPwm5Regs.TBPRD = Tempa;

EPwm5Regs.TBPRDHR = Tempb;

EPwm6Regs.TBPRD = Tempa;

EPwm6Regs.TBPRDHR = Tempb;

EPwm7Regs.TBPRD = Tempa;

EPwm7Regs.TBPRDHR = Tempb;

EPwm1Regs.TBPRD = Tempa;

EPwm1Regs.TBPRDHR = Tempb;

Hi,

Thanks for the code snippet. Please give our experts a few days to review this.

Thanks,

Ashwini

Hi

Can you please also send the definition for the struct ClaToCpuVars, definition of struct variable (mapping to a specific address space) as well as the linker command files for both projects. This will help us reproduce the test case.

Thanks,

Ashwini

define is:

//----------------------------------------

#pragma DATA_SECTION(ClaToCpuVars,"Cla1ToCpuMsgRAM");

volatile struct CLATOCPU_VARS ClaToCpuVars;

struct CLATOCPU_VARS //start @1480

{

float fLoopOutUse; //0x1480

float fPwmPrdMin; //0x1482

float fPwmPrd; //0x1484

float fPwmDuty; //0x1486

float fPwmTs; //0x1488

Uint16 u16PrdLoad; //0x148A

Uint16 u16PrdHrLoad; //0x148B

Uint16 u16Pwm1Cmpa; //0x148C

Uint16 u16Pwm1Cmpb; //0x148D

Uint16 u16Pwm2Cmpa; //0x148E

Uint16 u16Pwm2Cmpb; //0x148F

Uint16 u16Pwm3Cmpa; //0x1490

Uint16 u16Pwm3Cmpb; //0x1491

Uint16 u16Pwm4Cmpa; //0x1492

Uint16 u16Pwm4Cmpb; //0x1493

Uint16 u16Pwm5Cmpa; //0x1494

Uint16 u16Pwm5Cmpb; //0x1495

Uint16 u16Pwm6Cmpa; //0x1496

Uint16 u16Pwm6Cmpb; //0x1497

Uint16 u16PwmTBCTR1; //0x1498

Uint16 u16PwmTBCTR2; //0x1499

Uint16 u16PwmTBCTR3; //0x149A

};

extern volatile struct CLATOCPU_VARS ClaToCpuVars;

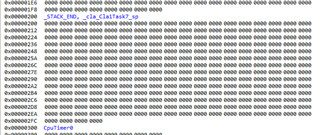

CMD file is:(from TI example)

CLA1_MSGRAMLOW : origin = 0x00001480, length = 0x00000080

CLA1_MSGRAMHIGH : origin = 0x00001500, length = 0x00000080

/*** application sw variables Structures ***/

//cla

Cla1ToCpuMsgRAM : > CLA1_MSGRAMLOW, PAGE = 1

CpuToCla1MsgRAM : > CLA1_MSGRAMHIGH, PAGE = 1

config:

Hi,

I was able to generate a testcase and a request has been created to analyze this. Our compiler team will investigate and get back to you.

Here is the link to the Jira, you can use this Jira ID if you need to follow up on this issue.

https://sir.ext.ti.com/jira/browse/EXT_EP-10429

Thanks,

Ashwini

Hi,

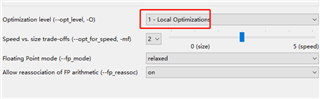

While the team is analysising this issue one suggestion is to change the optimization level from level -O0 to at least -O2.

Thanks,

Ashwini

thank you for your reply!

yes, my own solution is to use -O1 and can work well, However, I found that when the optimization level 1 was turned on, the execution pointer did not execute the code in order during the simulation step-by-step, which sometimes made debugging feel messy

Hi,

Good to know you are able to make progress. Thanks for the update.

Thanks,

Ashwini