For a 32-bit external memory, the F28335 External Interface (XINTF) had the capability of 16-bit access using XWE0n and/or XWE1n (see SPRU949D Table 2).

Does the F28388 EMIF have this capability?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

For a 32-bit external memory, the F28335 External Interface (XINTF) had the capability of 16-bit access using XWE0n and/or XWE1n (see SPRU949D Table 2).

Does the F28388 EMIF have this capability?

James,

Thanks for including the link to the table. It really helps to know exactly what you are referencing.

The EMIF can support 8-bit, 16-bit and 32-bit bus accesses. The EMIF has a different design lineage from XINTF so the 32-bit access is implemented in a different way. Instead of using XWE1n to indicate a 32-bit access, the EMIF allows the user to configure a different access mode for each CSn signal (memory region), and only one CSn signal is used per memory region.

I should point out that the EMIF address bus is 32-bit native and requires the mapping to shift when using 16-bit and 8-bit access:

-Tommy

Hi Tommy,

Thanks for responding. I understand the external memory could be designed with an 8-, 16-, or 32-bit data bus. I designed mine with a 32-bit data bus, but we would also like to store some 16-bit data in the same memory region. So, I have a couple follow-up questions:

1) In app note sprac96a Table 5, there is a related statement:

I DO want to use 16-bit reads and writes to my 32-bit memory, so does this statement imply that is possible, and related to using the DQMx signals?

2) If it is not possible to design the hardware to allow both 16- and 32-bit access to the same memory region, is there a way to tell the linker that the entire region only supports 32-bit access?

For example, I have a structure:

typedef struct{

float a;

int32 b;

int16 c;

int16 d;

}MYSTRUCT;

MYSTRUCT x;

If I store the above struct x in my 32-bit external memory, x.c and x.d do not work; writing to one overwrites the other, because the linker maps them as though 16-bit access is possible, but the actual result is that they are both stored at the same address.

I DO want to use 16-bit reads and writes to my 32-bit memory, so does this statement imply that is possible, and related to using the DQMx signals?

Sorry, I misread the XINTF XWEn signal to be the equivalent of EMIF CS in my prior post.

Yes, EMIF does support byte-level masking of the data bus so if you configure the CS space for 32-bit mode, the EMIF can still generate 16-bit operations by masking the invalid bytes using the DQMx signals. The EMIF implementation should be more straightforward for memories because they typically use compatible byte-enable signals.

2) If it is not possible to design the hardware to allow both 16- and 32-bit access to the same memory region, is there a way to tell the linker that the entire region only supports 32-bit access?

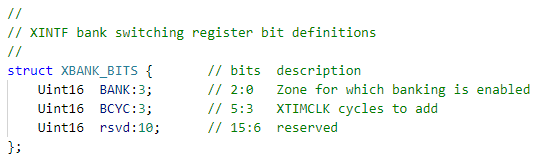

In such a scenario, bit-packing would be a straightforward method. This is used extensively in the header support files to allow programmatic access to individual register fields while preserving the memory map access mode of the underlying register: