Other Parts Discussed in Thread: C2000WARE

Hello,

1.I have set the DCC counters for PLLRAWCLKand INTOSC2 to check the tolerance of PLLRAWCLK .Does it make sense to also check the MCDCR.SYSREF_LOST_MCD_EN=1.?

Thanks

Ushma

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

1.I have set the DCC counters for PLLRAWCLKand INTOSC2 to check the tolerance of PLLRAWCLK .Does it make sense to also check the MCDCR.SYSREF_LOST_MCD_EN=1.?

Thanks

Ushma

Hi Ushma,

Just trying to understand what your set up looks like when using the DCC to check the tolerance of PLLRAWCLK. Also, what is the main intention here, is it to check the variation of INTOSC2 and what will be used to clock the PLL, is it the on board XTAL or INTOSC2? Once i have these information, i can have a better response or suggestion for you.

Best regards,

Joseph

HEllo ,

So basically i check the PLLRAWCLK with INTOSC2.The intention is also the same to check if the PLLRAWCLK which has source INTOSC2 lies with each other in tolerance limit .My question is does it make sense to also check the complete loss of INTOSC2 or MCDCR.SYSREF_LOST_MCD_EN=1? Or complete loss will be detected as a part of tolerance check.

I hope now it is clear.

Thanks

Ushma

Hi Ushma,

Thanks for providing more details but first wanted to answer the MCD question. MCD by default is enabled so anytime the primary clock in the system gets missing for some reason, the mechanism described in the TRM for clock detection takes over and there will be indications that this occurred through NMI or through some status bit in MCDSTS. For the intent of your function, you can poll MCDR..SYSREF_LOST_MCD_EN to see if it ever got set. For the internal oscillator, likelihood of clock missing is statistically very minimal as the internal clocks are always on. MCD will be more relevant if external clock is used since this is a way for the system to detect if there is a break in the clock path (X1) to the device or for some reason the power to the external clock gets interrupted.

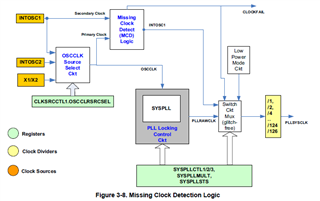

Now, let's refer to the figure below for reference:

If my understanding is correct, you are intending to have OSCCLK sourced by INTOSC2 so it will produce PLLRAWCLK, right? If this is the case whatever is the variation in INTOSC2 will be the exact variation in PLLRAWCLK (proportional to IMULT and the dividers) so you really cannot measure the variation if you are connecting INTOSC2 and PLLRAWCLK to the DCC counters. My suggestion is as follows:

- choose INTOSC2 as OSCCLK source to clock PLL to produce PLLRAWCLK

- Connect XTAL as your base timer for the DCC (DCC source 0) and PLLRAWCLK as DCC source 1.

XTAL (the on board crystal in the launchpad) is an independent, accurate, low variation clock source that can be used as reference to the DCC counter. Hope this makes sense.

Best regards,

Joseph

XTAL requires external Clock source , that i do not have .

Then i thougth of comparing the INTOSC1 and INTOSC2 with DCC1 and DCC0 PLLRAWCLK with INTOSC2.

Thanks

UShma

I thought you were using a Launchpad. It has an on-board XTAL that by default is connected to X1 and X2 pins. Anyway, you can also proceed with observing PLLRAWCLK variance by configuring INTOSC2 as OSCCLK to produce PLLRAWCLK as one input to DCC counter and INTOSC1 as the source for the other DCC counter.

Regards,

Joseph

Hello Joseph,

Are you talking about the Y2 crystal which is default present ?

Thanks

UShma

Hello Joseph,

i have two check now enabled one is MCDCR.SYSREF_LOST_MCD_EN=1 and the second is tolerance check with DCC(INTOSC2 as souce ) compared with INTOSC1.

For MCDCR.SYSREF_LOST_MCD_EN=1 i expect a NMI interrupt ( which there is no direct way to test except with DCC counters changing )

for DCC tolerance check i have enabled the DCC ISR , which comes when i change the DCC counters to test .

After enabling the CLKFAILCFG DCC0_ERROR_EN i expect in both the above cases , either complete loss or tolerance an NMI must come and not DCC_ISR. But it doent come DCC_ISR Comes still and when i disable it , no Interrupt Comes .I dont get it why ?

Also NMI Interrupt is enabled , i create other Errors then i get NMI Interrupt but not due to DCC module CLOCKFAIL .

Coud you please help me with it ?

Thanks

UShma

Hi Ushma,

To be clear, MCD logic is monitoring OSCCLK that feeds to PLL block. Diagram below:

MCD is outside of the DCC block. How are you emulating a missing clock?

Regards,

Joseph

Hello Joseph i am not using MCD instaed m using PLL refrence clock detection .I have disabled default enabled MCD logic.

Thats the point i cant do that when i am using PLL refrence clock detection.instaed i do with DCC counters.

Hi Ushma,

Ok, thanks for clarifying. Yes, it will be difficult to replicate/emulate the PLL reference clock lost since the INTOSC2 clock source is always on. Still checking on NMI assertion when CLKFAILCFG[DCC0_ERROR_EN] is active. By the way, can you let me know how you are generating a DCC0 ERROR generation? You might have already done theses checks but just confirming that you have initialized the interrupt module and vector tables using functions Interrupt_initModule() and Interrupt_intVectorTable() and mapped the DCC interrupt with functions Interrupt_register() and Interrupt_enable().

Thanks,

Joseph

Hello Joseph ,

i have tested DCC_Erro with Setting the counter 1 much more than the required .I am getting the DCC Interrupt but not NMI due to

CLKFAILCFG[DCC0_ERROR_EN]

Yes the sequence of my Code is as follows :

intitialise Interrupt module

Vector table

PLL init

CLKFAILCFG[DCC0_ERROR_EN] bit is set

Error craeted

NO NMI Inteerupt

Thanks

UShma

Hi Ushma,

We just tested the CLKFAILCFG DCC error functionality setting an NMI on the F280025 with no issues. Did you use your own code or did you use the C2000Ware codes?

Regards,

Joseph

Hi Ushma,

You can check the NMI functionality of CLKFAILCFG through DCC error by using the existing C2000Ware examples. I suggest to try this out first. Use C2000Ware example "dcc_ex1_single_shot_verification". What you can do is modify the counter value inside the function to force the DCC to generate an error., but before enabling DCC, you need to set CLKFAILCFG[DCCx_ERROR_EN]. Follow these steps and you should be able to generate an NMI.

Regards,

Joseph

Hello Joseph ,

Yes you are right before DCC enable this bit must be set i set after enable and then it was not successful.

Thanks for the support.it is really appreciable.

Thanks

UShma