HI expert,

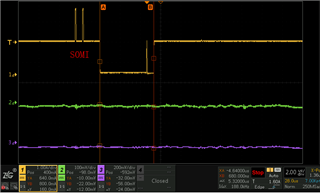

I use the new code modified from the code that has successfully implemented encoder reading data on F280049C-Launchpad, and the hardware resources are the control board designed by our company (the chip is F280049c).I tried to measure TXen(GPIO5) waveform, SOMI (GPIO10) waveform and Clks (GPIO3) waveform, but unfortunately only TXen waveform looks normal, SOMI looks abnormal, Clks waveform cannot be measured.Their waveforms are shown below:

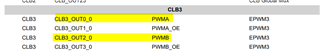

Figure 1: Waveform of TXen

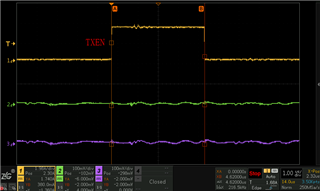

Figure 2: Waveform of SOMI

My configuration code is modified as follows: 1.GPIO port;2. XBAR;3.CLB, the specific code is as follows:

void tformat_setupGPIO(void)

{

//

// GPIO4 is SPI Clk slave

//

GPIO_setMasterCore(4, GPIO_CORE_CPU1);

GPIO_setPinConfig(GPIO_4_EPWM3A);

//

// GPIO8 is the SPISIMOA

//

GPIO_setMasterCore(8, GPIO_CORE_CPU1);

GPIO_setPinConfig(GPIO_8_SPISIMOA);

GPIO_setQualificationMode(8, GPIO_QUAL_ASYNC);

//

// GPIO10 is the SPISOMIA

//

GPIO_setMasterCore(10, GPIO_CORE_CPU1);

GPIO_setPinConfig(GPIO_10_SPISOMIA);

GPIO_setQualificationMode(10, GPIO_QUAL_ASYNC);

//

// GPIO3 is the SPICLKA

//

GPIO_setMasterCore(3, GPIO_CORE_CPU1);

GPIO_setPinConfig(GPIO_3_SPICLKA);

GPIO_setQualificationMode(3,GPIO_QUAL_ASYNC);

//

// GPIO57 is the SPISTEB

//

GPIO_setMasterCore(57, GPIO_CORE_CPU1);

GPIO_setPinConfig(GPIO_57_SPISTEA);

GPIO_setQualificationMode(57, GPIO_QUAL_ASYNC);

//

// GPIO5 is tformat TxEN

//

GPIO_setMasterCore(5, GPIO_CORE_CPU1);

GPIO_setPinConfig(GPIO_5_OUTPUTXBAR3);

}

void tformat_initCLBXBAR() {

XBAR_setCLBMuxConfig(XBAR_AUXSIG0, XBAR_CLB_MUX01_INPUTXBAR1);

XBAR_enableCLBMux(XBAR_AUXSIG0, XBAR_MUX01);

XBAR_setOutputMuxConfig(XBAR_OUTPUT3, XBAR_OUT_MUX09_CLB3_OUT4);

XBAR_enableOutputMux(XBAR_OUTPUT3, XBAR_MUX09);

}

The questions I would like to ask are as follows:

1.Is my configured correctly? Where are the problems likely to arise?

2.Maybe there is a problem with the hardware, so how should I check?