Dear team:

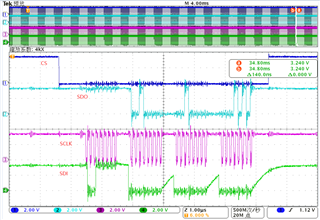

I configure McBSP as SPI to drive nflash. Nflash can respond to the instructions sent by DSP. The data waveform sent by nflash is correct, but the data read by DSP is incorrect,below are my code and waveforms.the data I read are 0x90,0xff,0x80,but the correct data should be 0x20,0x20,0x15。

void McBSPI_IO_Init(void)//SIP初始化

{

EALLOW;

GpioCtrlRegs.GPAPUD.bit.GPIO24 = 0; // Enable pull-up on GPIO24 (SPISIMO)

GpioCtrlRegs.GPAPUD.bit.GPIO25 = 0; // Enable pull-up on GPIO25 (SPISOMI)

GpioCtrlRegs.GPAPUD.bit.GPIO26 = 0; // Enable pull-up on GPIO26 (SPICLK)

GpioCtrlRegs.GPAQSEL2.bit.GPIO24 = 3; // Asynch input GPIO24 (SPISIMO)

GpioCtrlRegs.GPAQSEL2.bit.GPIO25 = 3; // Asynch input GPIO25 (SPISOMI)

GpioCtrlRegs.GPAQSEL2.bit.GPIO26 = 3; // Asynch input GPIO26 (SPICLK)

GpioCtrlRegs.GPAQSEL2.bit.GPIO27 = 3; // Asynch input GPIO27 (SPISTE)

//下面的值是3

GpioCtrlRegs.GPAMUX2.bit.GPIO24 = 3; // Configure GPIO24 as SPISIMO

GpioCtrlRegs.GPAMUX2.bit.GPIO25 = 3; // Configure GPIO25 as SPISOMI

GpioCtrlRegs.GPAMUX2.bit.GPIO26 = 3; // Configure GPIO26 as SPICLK

//Configure GPIO27 as SPISTEA

GpioCtrlRegs.GPAPUD.bit.GPIO27 = 0;// Enable pullup

GpioDataRegs.GPASET.bit.GPIO27 = 1; // Load output latch

GpioCtrlRegs.GPAMUX2.bit.GPIO27 = 0; //

GpioCtrlRegs.GPADIR.bit.GPIO27 = 1; // GPIO27 = output

EDIS;

}

void MCBSP_SPI_Init(void)//SPI初始化

{

McBSPI_IO_Init();//IO初始化

EALLOW;

SysCtrlRegs.PCLKCR0.bit.MCBSPBENCLK = 1;

EDIS;

//SET McBSP-B to SPI master mode with no cycle clk delay

// McBSP-B register settings

McbspbRegs.SPCR2.all=0x0000; // Reset FS generator, sample rate generator & transmitter

McbspbRegs.SPCR1.all=0x0000; // Reset Receiver, Right justify word, Digital loopback dis.

//McbspbRegs.PCR.all=0x0F08; //(CLKXM=CLKRM=FSXM=FSRM= 1, FSXP = 1)

McbspbRegs.SPCR1.bit.RJUST = 0;

McbspbRegs.PCR.bit.FSXM=1;//FSX generate by in ternal

McbspbRegs.PCR.bit.CLKXM=1;// spi master mode 1

McbspbRegs.PCR.bit.FSXP=1;// FSX active low

McbspbRegs.PCR.bit.CLKXP=1;// rising edge of clk,output data valid

McbspbRegs.PCR.bit.SCLKME=0;// LSPCLK

McbspbRegs.PCR.bit.FSRM=1;//FSR generate by internal

McbspbRegs.PCR.bit.CLKRM=1;// CLK R OUTPUT

McbspbRegs.PCR.bit.FSRP=1;// FSR active low

McbspbRegs.PCR.bit.CLKRP=1;// falling edge of clk,input data valid

McbspbRegs.PCR.bit.SCLKME = 0;

McbspbRegs.SPCR1.bit.DLB = 0;

McbspbRegs.SPCR1.bit.CLKSTP = 0x03;// spi mode with clk delay

McbspbRegs.SPCR2.bit.FREE=1;

McbspbRegs.SPCR2.bit.SOFT=1;

McbspbRegs.RCR2.bit.RPHASE=0;//single frame phase

McbspbRegs.RCR2.bit.RCOMPAND=0;//any data size MSB first

McbspbRegs.RCR2.bit.RDATDLY=01;// FSX setup time 1 in master mode. 0 for slave mode (Receive)

McbspbRegs.XCR2.bit.XPHASE=0;//single frame phase

McbspbRegs.XCR2.bit.XCOMPAND=0;//

McbspbRegs.XCR2.bit.XDATDLY=01;// FSX setup time 1 in master mode. 0 for slave mode (Transmit)

McbspbRegs.RCR1.bit.RFRLEN1=0;// one word per frame

McbspbRegs.RCR1.bit.RWDLEN1=0;// 16-bit word

McbspbRegs.XCR1.bit.XFRLEN1=0;//one word per frame

McbspbRegs.XCR1.bit.XWDLEN1=0;// 16-bit word

// McbspbRegs.SRGR2.all=0x2000; // CLKSM=1, FPER = 1 CLKG periods

McbspbRegs.SRGR2.bit.GSYNC=0;//

McbspbRegs.SRGR2.bit.CLKSM=1;//lspclk

McbspbRegs.SRGR2.bit.FSGM=0;//FSG generate when data are copied to XSR1,2

McbspbRegs.SRGR2.bit.FPER=0x02;//no used

//McbspbRegs.SRGR1.all= 0x0F0F;// Frame Width = 1 CLKG period, CLKGDV=16

McbspbRegs.SRGR1.bit.CLKGDV=0x3;// LSPCLK/3 (0x5f,过采样有效,小于此值过采样值偏低不准)

McbspbRegs.SRGR1.bit.FWID=0x0f;//FSG Pulse width is 16

McbspbRegs.SPCR2.bit.GRST=1;// Enable the sample rate generator

delay_loop(); // Wait at least 2 SRG clock cycles

McbspbRegs.SPCR2.bit.XRST=1;// Release TX from Reset

McbspbRegs.SPCR1.bit.RRST=1;// Release RX from Reset

McbspbRegs.SPCR2.bit.FRST=1;// Frame Sync Generator reset

}

void m25p16_readID(void)

{

Select_Flash();

while(McbspbRegs.SPCR2.bit.XRDY == 0);

McbspbRegs.DXR1.all = RDID&0x00FF;

while(McbspbRegs.SPCR2.bit.XRDY == 0);

McbspbRegs.DXR1.all = 0xFF;

while( McbspbRegs.SPCR1.bit.RRDY == 0 ) ;

temp[0] = McbspbRegs.DRR1.all;

while(McbspbRegs.SPCR2.bit.XRDY == 0);

McbspbRegs.DXR1.all = 0xFF;

while( McbspbRegs.SPCR1.bit.RRDY == 0 ) ;

temp[1] = McbspbRegs.DRR1.all;

while(McbspbRegs.SPCR2.bit.XRDY == 0);

McbspbRegs.DXR1.all = 0xFF;

while( McbspbRegs.SPCR1.bit.RRDY == 0 ) ;

temp[2] = McbspbRegs.DRR1.all;

DELAY_US(3);

NotSelect_Flash();

}