Other Parts Discussed in Thread: C2000WARE

Hello,

I'm using CPU1 and CPU2 on TMS320F28379D

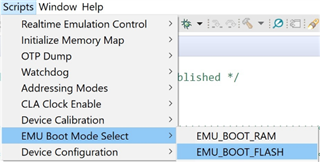

In my software, I want to reprogram FLASH for CPU1 and CPU2 with an HEX file on a SD card (using SPI-A).

For information, on a previous program, I used only CPU1 and this function (FLASH reprogramming with SD card) works fine.

The reprogramming process is as follow :

- Read HEX file information's

- Erase CPU1 Flash sectors

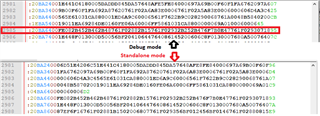

- Write HEX file data's in FLASH

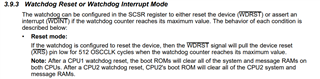

- Reboot CPU1 with watchdog

Below how I want to proceed :

- In normal state, CPU1 program and CPU2 program are synchronized with IPCs flags.

- If CPU1 reprogramming is in progress; CPU2 is in "idle" state. SPI-A is drived by CPU1.

- When CPU1 reprogramming is done, CPU1 send an IPC (IPC0) flag to CPU2 to start reprogramming (interrupt on CPU2),change SPI-A ownership (CPU1 -> CPU2) then reboot.

- CPU2 reprogramming is in progress; CPU1 is in "idle" state. SPI-A is drived by CPU2.

- When CPU2 reprogramming is done, CPU2 reboot.

- When both core will reboot, we will be in normal state.

I can reprogram CPU1 FLASH correctly, but I have some questions for CPU2 reprogramming :

- During CPU1 Flash programming process, SPI-A is drived by CPU1. I tried to change SPI-A ownership to CPU2 after CPU1 reboot, but it seems it doesn't works. Why ?

- After CPU1 programming and reboot, I already have "Illegal_ISR", maybe it's due to the Debug mode on Code Composer after a reboot. How can I debug CPU2 program ?

Regards,