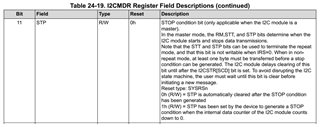

I am doing some experiments with the I2C peripheral to understand it better. When in non-repeat mode master transmitter, I enable STT and STP bits after putting data in TX FIFO. The code is as follows:

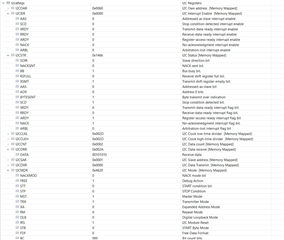

If the microcontroller recieves NACK from slave receiver (line 17 breakpoint), I see that SDA line is high, SCL line stays low, BB = 1, MST = 1, which means STOP condition has not been generated. But STP = 0, STT = 0. The register snapshot at line 17 is below:

STOP condition is generated only when STP is set once again (line 20).

I did not find any mention in TRM about STP bit being reset due to NACK received

Could anyone please give a clarification regarding this behaviour?