I am doing some experiments with the I2C peripheral to understand it better. When in non-repeat mode master transmitter, I enable STT and STP bits after putting data in TX FIFO. The code is as follows:

I2C_setSlaveAddress(I2CA_BASE, 0x01);

//Set as master transmitter

I2C_setConfig(I2CA_BASE, (I2C_MASTER_SEND_MODE));

//Setup how many bytes to send

I2C_setDataCount(I2CA_BASE, 0x02);

//Configure fifo data for EEPROM address

I2C_putData(I2CA_BASE, (address>>8) & 0xFF);

I2C_putData(I2CA_BASE, address & 0xFF);

I2C_sendStartCondition(I2CA_BASE);

I2C_sendStopCondition(I2CA_BASE);

DEVICE_DELAY_US(150U);

if(I2C_getStatus(I2CA_BASE) & I2C_STR_NACK)

{

I2C_clearStatus(I2CA_BASE, I2C_STS_NO_ACK);

I2C_sendStopCondition(I2CA_BASE);

I2C_disableFIFO(I2CA_BASE);

I2C_enableFIFO(I2CA_BASE);

SysCtl_delay(2000);

WaitCount++;

}

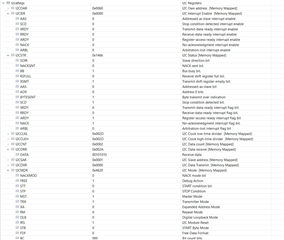

If the microcontroller recieves NACK from slave receiver (line 17 breakpoint), I see that SDA line is high, SCL line stays low, BB = 1, MST = 1, which means STOP condition has not been generated. But STP = 0, STT = 0. The register snapshot at line 17 is below:

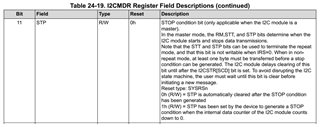

STOP condition is generated only when STP is set once again (line 20).

I did not find any mention in TRM about STP bit being reset due to NACK received

Could anyone please give a clarification regarding this behaviour?