Part Number: TMS320F28379D

Other Parts Discussed in Thread: C2000WARE

Hello,

I am using the following empty project inside C2000Ware_3_04_00_00.

C:\C2000Ware_3_04_00_00\driverlib\f2837xd\examples\dual\empty_projects

After I wrote some code in the project, I started getting the following errors.

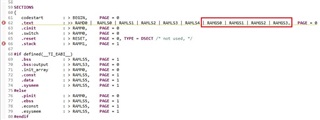

I added the "RAMGS0 | RAMGS1 | RAMGS2 | RAMGS3" sections to the project because of insufficient RAM.

The "2837xD_RAM_lnk_cpu1.cmd" file of my project is attached.

How can we solve this error?

Thanks,

Sinan.