Part Number: TMDSDOCK28335

Other Parts Discussed in Thread: TMS320F28335, C2000WARE

Hi all,

I'm having trouble with Flash programming on TMS320F28335.

Now I'm using a C2000 TMS320F28335, and I want to copy the program from Flash to RAM so that the DSP can work stand alone.

However, the DSP does not work when I press the Debug button in Code Composer Studio (CCS) and write the program to the DSP : PWM waveforms cannot be observed when I run the program.

The CCS debug window shows "ILLEGAL_ISR() at DSP2833x_DefaultIsr.c:154 0x338044", but I can't figure out where the problem is.

I attached some picture and the CCS projects that we are currently considering because it is difficult to explain the situation in writing. Please find it.

```

Projects.zip

- DAB_40V_Ver7 : Write to RAM。It works fine.

- DAB_40V_Ver8 : Modify above project to write flash. It cannot work.

Environment1, 2.PNG : Specific environments on CCS

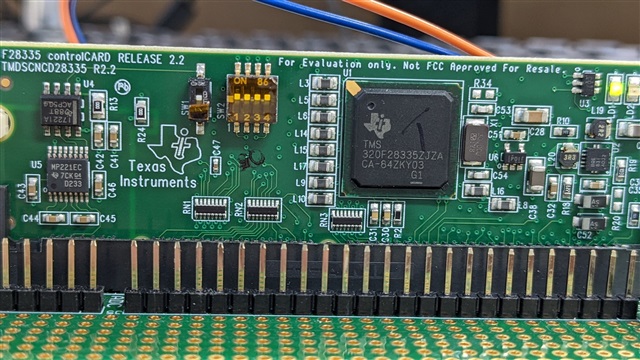

Pin_settings.jpg : A pin settings on control CARD of F28335

Result.PNG : Debug window on CCS

Waveform on GPIO 00 by DAB_40V_ver7.jpg

```

And I used CCS(9.3.0.00012).

I want any advice to fix this issue.

Best Regards,

Eto