Part Number: TMS320F28388S

Other Parts Discussed in Thread: C2000WARE, SYSCONFIG

Hi all,

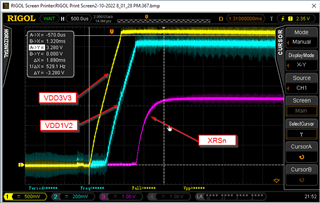

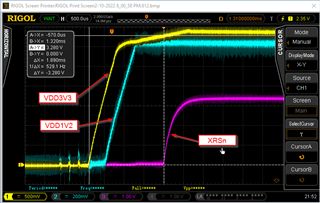

I am trying to upload a code in flash on a F28388S. The code runs after programming but does not run if I power cycle the uC.

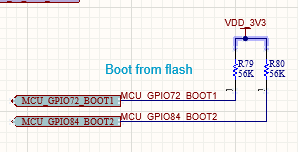

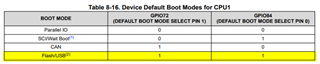

It is a custom board with a F28388S. The two GPIO 72 and 84 are tied to 3V3 to boot in Flash:

The code is just toggling GPIO output:

Building in RAM everything is OK.

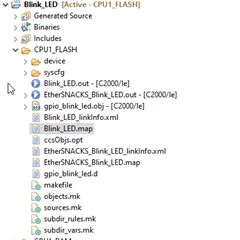

Building in FLASH for the first time, I receive an error: "line 33: fatal error #1965: cannot open source file "board.h"", then I re-try to build again, the error disappears **** Build Finished ****. After programming the code runs, if I reset the power the stop does not run.

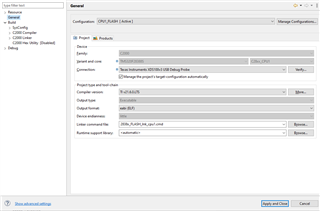

I am using CCS V11.1.0.00011

Project properties are configured for F28388S CPU1 connection XDS100V3 (I am using the OLIMEX XDS100v3):

Any idea what is the issue? I am pretty sure it is related to the error the first time I build in FLASH.

Thank you

and choose my GPIO.

and choose my GPIO.