TMS320F2812 is designed to boot from external boot space. Initially the bootloader is loaded to FPGA Dual port ram by ARM processor. The boot vector is perfectly fetched from FPGA using CS6&7 and it jumps to the bootloader location (using CS2) in FPGA dual port ram and starts file fetch. Our observation is once the boot-loader is fetched and during its execution the CS2 stops transition and stay high. This issue occurs randomly in some PCBAs only. Is there any known issues and solutions similar to this?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

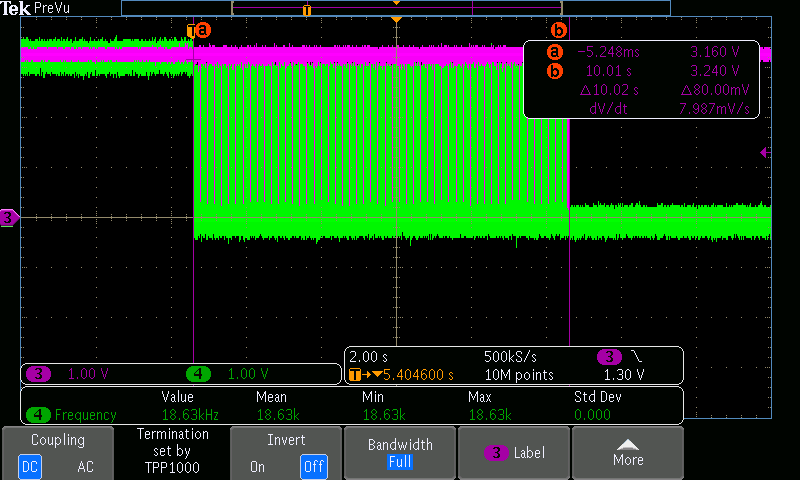

PFA, We were able to solve the above issues with some code changes. Our observation is on all the working PCBAs after bootloader fetching, the execution starts at a particular time in our case it is 190mS. In one PCBA at this 190mS instead of file execution, again the boot vector fetch is occurring but vector fetch address is wrong after first fetch. This retry happens for 10seconds and CS6&7 stays high and CS2 stays low. What could be the reason for this retry? (Note:Green-CS2,Pink-CS6&7)

PFA, We were able to solve the above issues with some code changes. Our observation is on all the working PCBAs after bootloader fetching, the execution starts at a particular time in our case it is 190mS. In one PCBA at this 190mS instead of file execution, again the boot vector fetch is occurring but vector fetch address is wrong after first fetch. This retry happens for 10seconds and CS6&7 stays high and CS2 stays low. What could be the reason for this retry? (Note:Green-CS2,Pink-CS6&7)