Hi team.

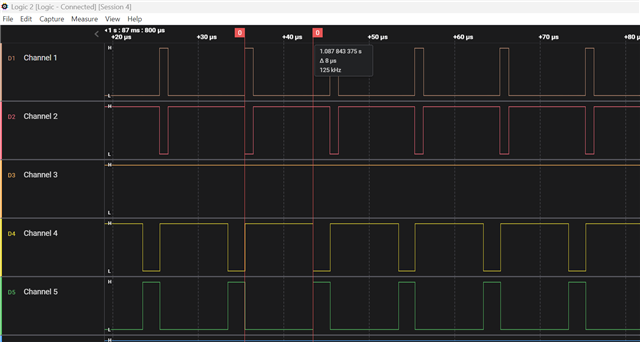

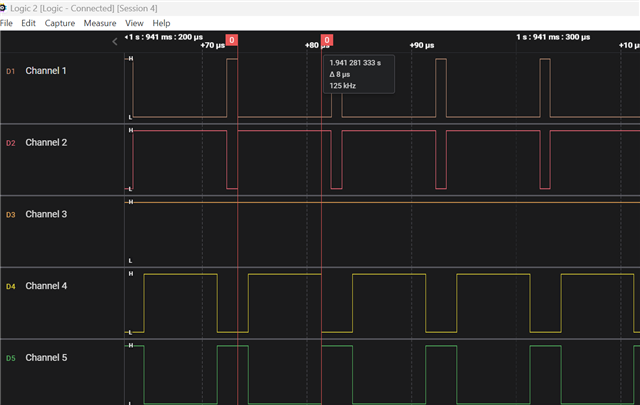

Is there any way that I can introduce phase shift between two sawtooth's (EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; and EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP;) that are used in PWM.

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; // Count up

EPwm1Regs.TBPRD = EPWM1_TIMER_TBPRD; // Set timer period

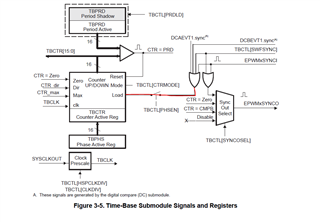

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Disable phase loading

EPwm1Regs.TBPHS.half.TBPHS = 0x0000; // Phase is 0

EPwm1Regs.TBCTR = 0x0000; // Clear counter

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV2; // Clock ratio to SYSCLKOUT

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV2;

//Other things are removed to keep the code simple

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; // Count up

EPwm2Regs.TBPRD = EPWM2_TIMER_TBPRD; // Set timer period

EPwm2Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Disable phase loading

EPwm2Regs.TBPHS.half.TBPHS = 0x0000; // Phase is 0

EPwm2Regs.TBCTR = 0x0000; // Clear counter

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV2; // Clock ratio to SYSCLKOUT

EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV2;