Part Number: TMS320F280049C

Other Parts Discussed in Thread: C2000WARE, SYSBIOS

Hi TI Team,

I have an application where the ADCC1 conversion complete drives DMA1 for data transfer. When DMA 1 transfer is complete it fires the DMA CH1 interrupt to perform timing critical processing. We are running this interrupt outside the OS as an NMI to make sure it does not get preempted or delayed.

I am now trying to add a system protection Interrupt attached to XINT1, and want this one to run at the highest priority. I configured this one inside the OS. Since XINT1 is supposed to be of higher priority than DMA and SCI I would have expected this interrupt would preempt those of lower priority and run first. But this was not the case.

I suspected that because I have the DMA interrupt as NMI that it cannot be preempted. Therefore, I remove the NMI setting and see an extra processing time hit I assume due to OS overhead, but to make things worst, if I start communicating to the system over my serial port on SCI-B (using interrupts) then the frequency and durations of my critical ISR become unstable.

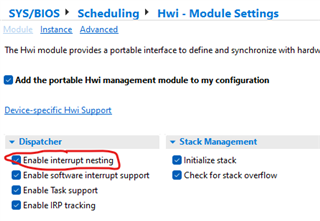

My first thought was to move the DMA interrupt inside the OS, assuming that the OS would then control who goes next based on the hardware priority with the enable nesting flag set. But this did not work.

A few other postings just point to this 2020 writeup on the topic: C28x Interrupt Nesting. However, this is not very clear, and do not use driverlib functions.

The posting suggests that the ISR functions need to be modified so that they are polite and yield the processor to other interrupts, but no matter what I tried I still get the same odd results.

In a nutshell the posting above mentions this sequence:

uint16_dtc TempPIEIER;

TempPIEIER = PieCtrlRegs.PIEIER2.all; // Save PIEIER register for later

IER |= 0x0002; // Set global priority by adjusting IER

IER &= 0x0002;

PieCtrlRegs.PIEIER9.all &= 0x0002; // Set group priority by adjusting PIEIER2 to allow INT2.2 to interrupt current ISR

PieCtrlRegs.PIEACK.all = 0xFFFF; // Enable PIE interrupts

asm(" NOP"); // Wait one cycle

EINT; // Clear INTM to enable interrupts

// Here do my interrupt code

...

DINT;

PieCtrlRegs.PIEIER2.all = TempPIEIER;

Can you guys provide an example using driverlib to achieve the desired behavior?

XINT1 should be top priority

DMA1 interrupt should be second

The rest should follow (SCI and I2C)

I added the code below into my SCI-B RX and TX ISRs following the comments on the sample code, but still get the same results. My DMA 1 interrupt inside the OS (not NMI) is still been preempted by SCI-B communications.

Interrupt_enableInCPU(INTERRUPT_CPU_INT7);

Interrupt_disableInCPU(INTERRUPT_CPU_INT9);

Interrupt_enablePIE();

Interrupt_enableMaster();

If I move both XINT1 and DMA1 outside the OS as NMI will their priorities be respected?