Part Number: TMS320F280041

Other Parts Discussed in Thread: SYSCONFIG

Hi,all

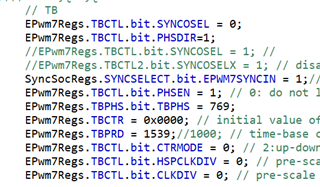

I am try to achieve a 180° phase shift of EPWM7 relative to EPWM6 by adding a phase-shift angle,but just congigure the PHSEN and TBPHS does not serve my purpose.What other registers do I need to configure?

The waveform is as follows,CH5/CH7-EPWM6;CH6/CH8-EPWM7.I want the waveforms of EPWM6 and EPWM7 to complement each other after phase shifting.