Other Parts Discussed in Thread: SYSCONFIG

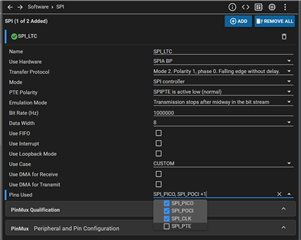

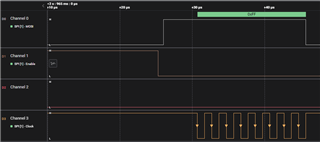

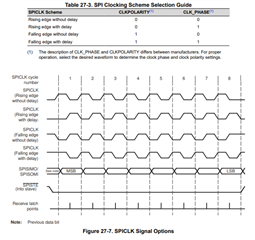

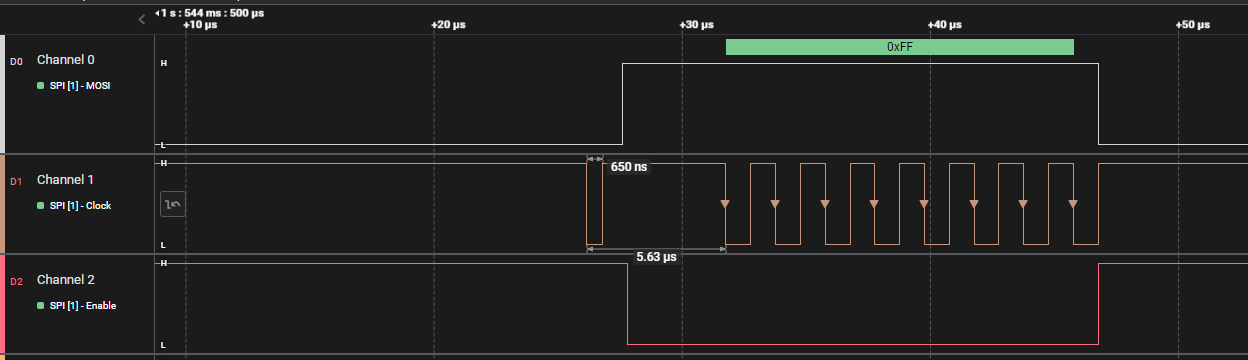

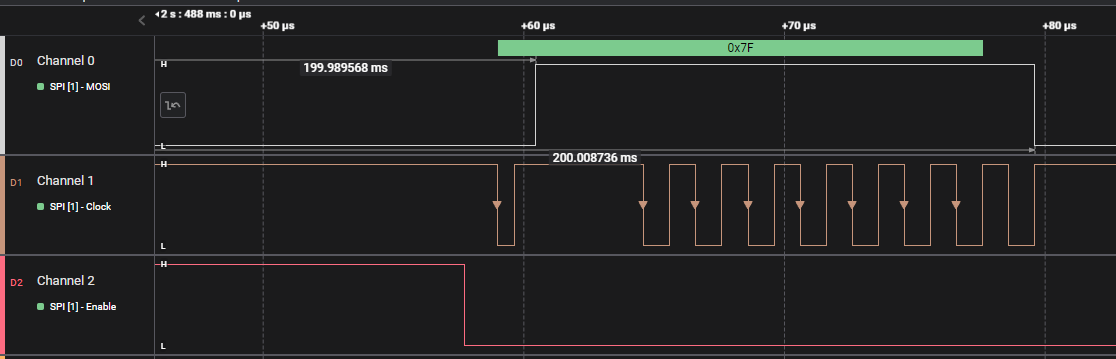

I have configured SPI in 3 pin mode using sysconfig. I selected the use case as custom and used only POCI, PICO and CLK pins. However, when I manually make the CS pin low, and use any driverlib function to read or write SPI data, there's an initial clock pulse that makes the data read erroneous. This pulse is also present in 4 pin mode, but in that mode the CS pin is pulled low only after that initial pulse is over. How can I stop this from happening?

4 pin mode

3 pin mode