- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Experts,

I am here asking for my customer.

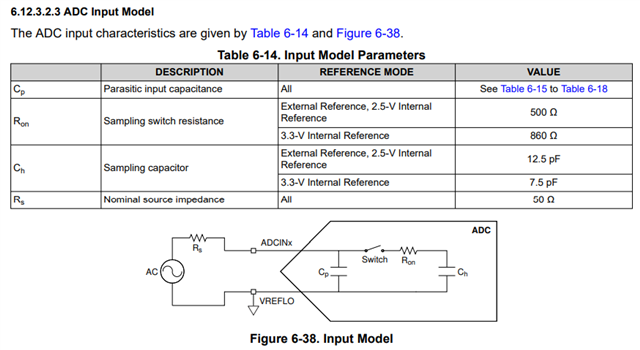

Customer are using round robin SOC Priority, configure 6 Channels on one ADC module. And they concerned that SOC0 and SOC1 adjacent sampling channels, when SOC0 done and SOC1 start, does the charge on the Ch/7.5PF capacitor completely released? Or it still means that the Ch charge still exists, but there is a hardware mechanism to ensure the accuracy of continuous multiple channel switching for sampling. Thanks.

Hi Experts,

Before SOC1 start, does the charge on the Ch/7.5PF capacitor completely released w/SOC0?

Hi Experts,

I want to double confirm with you, the Type-5 ADC in F2800137/157 are the same as the Type-3 ADC circuit. Right?

Hi Experts,

We want to confirm with you, the Type-5 ADC IP is the same as ADS7826? Thanks.

Hi Shaoxing,

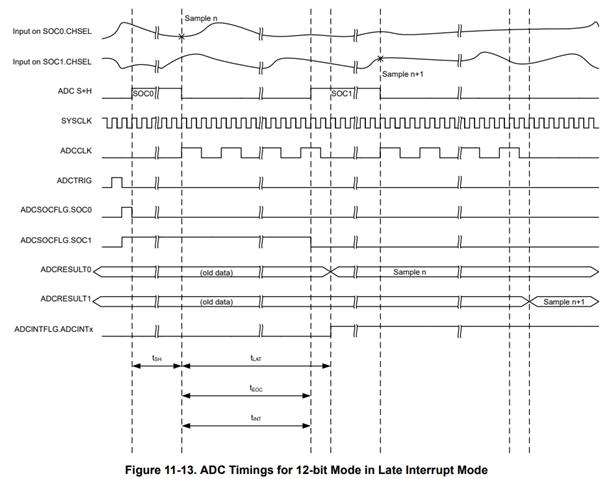

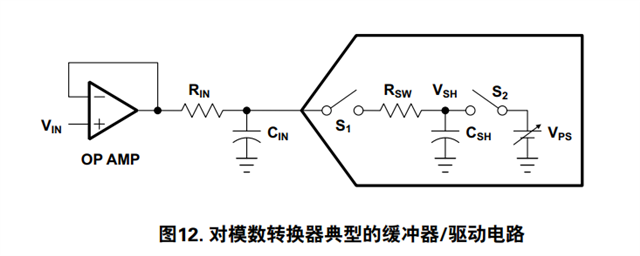

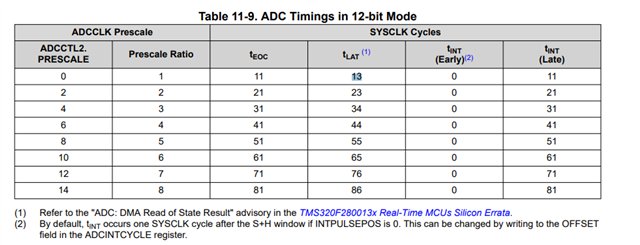

Just to be on the same page, where are you referring the ADC types from? ADS7826 is not a C2000 device so it will for sure not use the C2000 ADC SARs. As for the sampling capacitor inside the SAR, the switching is will only happen when the trigger is ready from the SOC configuration and remains on (charging) for the duration specified by ACQPS + 1 (or SH time). It will automatically open after the quration of SH time and then the SAR will convert for the duration of tLAT in the timing digaram. The capacitor will remain open for the duration of tLAT. It will only close nd charge if a trigger is received.

Regards,

Joseph

Hi Joseph,

Hi Shaoxing,

After tLAT, the charge on the SH cap would be discharged inside the SAR module when conversion completes.

Regards,

Joseph

Hi Joseph,

After tLAT, the charge on the SH cap would be discharged inside the SAR module when conversion completes,- want to confirm with you, does the SH cap discharged completely when the next SOC starts? Thanks.

Hi Shaoxing,

After looking closely at the SAR implementation on the F280013x device, i realized that the sampling capacitor does not actually discharge after tLAT. To enable discharge of the sampling capacitor, users can either sample on intrnal VREFLO channels (A13 for ADC-A ore C13 for ADC-C). If ACQPS (or SH time) is sufficient, then sampling capacitor will charge (equalize) to the same level as the analog input signal even if the sampling capacitor is not fully discharged on the succeeding sample/conversion cycle. F280013x does not have a feature to automatically discharge the sampling capacitor but this feature is added in our next generation of devices.

In summary, to mitigate the issue of sampling capacitor not fully discharged:

Regards,

Joseph

Hi Shaoxing,

Closing this post. Let's continue discussions over email.

Thanks,

Joseph