Part Number: TMS320F280049C

Hello,

We are facing a problem of distortion in the sinusoidal output voltage of half bridge inverter using ePWM module on F280049.

A sinusoidal PWM is generated with complementary outputs of ePWM2A and ePWM2B outputs. Following are the code related snippets:

/*------------------------------------------------------------------------------------------------------------------------------------------*/

/*--PWM initialization--*/

EALLOW;

// Time Base SubModule Registers

EPWM_setPeriodLoadMode(base,EPWM_PERIOD_SHADOW_LOAD);

EPWM_setTimeBaseCounterMode(base,EPWM_COUNTER_MODE_UP_DOWN);

EPWM_disablePhaseShiftLoad(base);

EPWM_setClockPrescaler(base,EPWM_CLOCK_DIVIDER_1,EPWM_HSCLOCK_DIVIDER_1);

EPWM_setTimeBasePeriod(base,pwm_period_ticks);//Set PWM period

EPWM_setTimeBaseCounter(base,0);

EPWM_setPhaseShift(base,0);

// Counter Compare Submodule Registers

EPWM_setCounterCompareValue(base,EPWM_COUNTER_COMPARE_A,0);

EPWM_setCounterCompareValue(base,EPWM_COUNTER_COMPARE_B,0);

EPWM_setCounterCompareShadowLoadMode(base,EPWM_COUNTER_COMPARE_A,EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_setCounterCompareShadowLoadMode(base,EPWM_COUNTER_COMPARE_B,EPWM_COMP_LOAD_ON_CNTR_ZERO);

// set as immediate mode

EPWM_disableCounterCompareShadowLoadMode(base,EPWM_COUNTER_COMPARE_A);

EPWM_disableCounterCompareShadowLoadMode(base,EPWM_COUNTER_COMPARE_B);

// Action Qualifier SubModule Registers

// to start don't configure the PWM to do anything

HWREGH(base + EPWM_O_AQCTLA) =0 ;

HWREGH(base + EPWM_O_AQCTLB) =0 ;

EPWM_setActionQualifierAction(base, EPWM_AQ_OUTPUT_A ,

EPWM_AQ_OUTPUT_HIGH, EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPA);

EPWM_setActionQualifierAction(base, EPWM_AQ_OUTPUT_A ,

EPWM_AQ_OUTPUT_LOW, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPA);

// Complementary PWMs, PWMA source for OUTA and OUTB

EPWM_setDeadBandCounterClock(base,EPWM_DB_COUNTER_CLOCK_FULL_CYCLE);

EPWM_setRisingEdgeDelayCount(base,pwm_dbred_ticks);

EPWM_setFallingEdgeDelayCount(base,pwm_dbred_ticks);

EPWM_setDeadBandDelayMode(base,EPWM_DB_RED,true);//Register DBCTL bits OUT_MODE; S1=1-> RED in A signal path

EPWM_setDeadBandDelayMode(base,EPWM_DB_FED,true);//Register DBCTL bits OUT_MODE; S0=1-> FED in B signal path

EPWM_setRisingEdgeDeadBandDelayInput(base,EPWM_DB_INPUT_EPWMA);//Register DBCTL bits IN_MODE; S4=0 -> input signal ePWMA for RED and FED

EPWM_setFallingEdgeDeadBandDelayInput(base,EPWM_DB_INPUT_EPWMA);//Reg DBCTL bit DEDB_MODE(S8)=0; IN_MODE S5=0-> input signal ePWMA for FED

EPWM_setDeadBandDelayPolarity(base,EPWM_DB_FED,EPWM_DB_POLARITY_ACTIVE_LOW);//Reg DBCTL bit POLSEL(S3)=1 ->OUTB inverted

EPWM_setDeadBandDelayPolarity(base,EPWM_DB_RED,EPWM_DB_POLARITY_ACTIVE_HIGH);//Reg DBCTL bit POLSEL(S2)=0->OUTA not inverted

/*--PWM generation in ISR in open loop--*/

invDutyPU = (spll1.sine) * invVoRefInst * 0.8;

invDutyPU= (invDutyPU>(float)(0.8))?(float)(0.8):invDutyPU;

invDutyPU= (invDutyPU<(float)(-0.8))?(float)(-0.8):invDutyPU;

EPWM_setCounterCompareValue(INV_PWM_BASE, EPWM_COUNTER_COMPARE_A, ( (uint16_t) (pwmDutyVar + (pwmDutyVar*invDutyPU) ) ));//pwmDutyVar is half the PWM period count

/*------------------------------------------------------------------------------------------------------------------------------------------*/

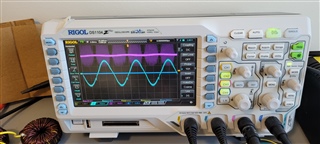

Please see the output voltage waveform generated using above code (Blue waveform in the attached image). There appears a small distortion in the waveform in the negative half cycle. To be sure that the distortion is due to PWM generated from PWM module, we exchanged the inverter transistor driver outputs keeping the inputs same. Then the distortion appears in the positive half cycle.

Can you please help us to understand if this is related to PWM generation as we suspect.

With regards,

Vijay