Part Number: TMS320F28388D

Other Parts Discussed in Thread: DP83640,

Hello!

We have a TMS320F28388D ControlCARD (with onboard PHY using MII interface) and a custom PCB with TMS320F28388D and a TI DP83640 PHY wired with RMII interface. I can't get the latter to work, for example with the ethernet_ex4_ptp_basic_master. Can you help me making the necessary changes for RMII and debugging why it is not working?

What I did:

- First, I got the example 'ethernet_ex4_ptp_basic_master' running on the ControlCARD. I only had to define the macro "ETHERNET" in the cm_common_config_c28x project. I can see the PTP messages in Wireshark each second, as expected.

- Then I modified the pins for our custom hardware for RMII:

//

// Configure the GPIOs for ETHERNET.

//

//

// MDIO Signals

//

GPIO_setPinConfig(GPIO_105_ENET_MDIO_CLK); // PHY: MDC

GPIO_setPinConfig(GPIO_106_ENET_MDIO_DATA); // PHY: MDIO

//

// Use this only for RMII Mode

GPIO_setPinConfig(GPIO_73_ENET_RMII_CLK); //PHY: X1

//

//RMII Signals

//

GPIO_setPinConfig(GPIO_75_ENET_MII_TX_DATA0); //PHY: TXD_0

GPIO_setPinConfig(GPIO_122_ENET_MII_TX_DATA1); //PHY: TXD_1

GPIO_setPinConfig(GPIO_118_ENET_MII_TX_EN); //PHY: TX_EN

GPIO_setPinConfig(GPIO_114_ENET_MII_RX_DATA0); //PHY: RXD_0

GPIO_setPinConfig(GPIO_115_ENET_MII_RX_DATA1); //PHY: RXD_1

GPIO_setPinConfig(GPIO_113_ENET_MII_RX_ERR); //PHY: RX_ERR

GPIO_setPinConfig(GPIO_112_ENET_MII_RX_DV); //PHY: CRS/CRS_DV - Additionally, I had to define USE_20MHZ_XTAL because that is what our custom board has.

- Finally, I changed this line in ethernet_ex4_ptp_basic_master

initInterfaceConfig.phyMode = ETHERNET_SS_PHY_INTF_SEL_RMII;

and added

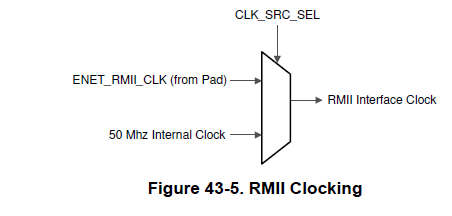

initInterfaceConfig.clockSel = ETHERNET_SS_CLK_SRC_INTERNAL;

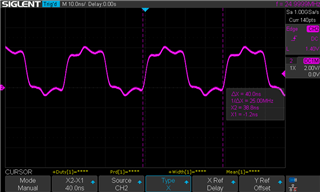

Via SMI I can verify that a 100Mbit full-duplex link is negotiated (VALID LINK flag goes high). I can also measure activity on TX_EN, TXD_0, TXD_1 (every second as expected by the example) and RMII_CLK/X0. But, alas, nothing can be seen in Wireshark.

Did I miss to something when migrating the code from MII to RMII?

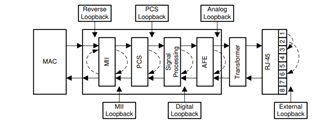

Are the any registers of the EMAC that I can use to debug the problem?

We did check all the strapping pins of the PHY and verified the configuration via SMI (RMII mode, RMII Slave Clock Mode).

We would be grateful for any hints.

Best regards, Nils