- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

• Background:

during LLC charging process; ePWM3&4 driving LLC H-Bridge; PWM frequency 80k~150k(set by software); resonant operating frequency 90kHz;

The waveform is captured by monitor the C2000 device's ePWM output pins, an isolation is added between MOS driver and C2000:

(The left pins pointed by the red arrow are connected to C2000)

MOS driver:

ePWM configure code:

void UserSetEPWM()

{

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0;

EDIS;

EALLOW;

GpioCtrlRegs.GPHAMSEL.bit.GPIO242 = 0;

GpioCtrlRegs.GPHQSEL2.bit.GPIO242 = 3;

InputXbarRegs.INPUT1SELECT = 242;

GpioCtrlRegs.GPHLOCK.bit.GPIO242 = 1;

GpioCtrlRegs.GPHCR.bit.GPIO242 = 1;

InputXbarRegs.INPUTSELECTLOCK.bit.INPUT1SELECT = 1;

EPwm1Regs.TZSEL.bit.OSHT1 = TZ_ENABLE;

EPwm2Regs.TZSEL.bit.OSHT1 = TZ_ENABLE;

EPwm3Regs.TZSEL.bit.OSHT1 = TZ_ENABLE;

EPwm4Regs.TZSEL.bit.OSHT1 = TZ_ENABLE;

EPwm1Regs.TZSEL.bit.OSHT5 = TZ_ENABLE;

EPwm2Regs.TZSEL.bit.OSHT5 = TZ_ENABLE;

EPwm3Regs.TZSEL.bit.OSHT5 = TZ_ENABLE;

EPwm4Regs.TZSEL.bit.OSHT5 = TZ_ENABLE;

EPwm1Regs.TZSEL.bit.OSHT6 = TZ_ENABLE;

EPwm2Regs.TZSEL.bit.OSHT6 = TZ_ENABLE;

EPwm3Regs.TZSEL.bit.OSHT6 = TZ_ENABLE;

EPwm4Regs.TZSEL.bit.OSHT6 = TZ_ENABLE;

EPwm1Regs.TZCTL.bit.TZA = TZ_FORCE_LO;

EPwm1Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm2Regs.TZCTL.bit.TZA = TZ_FORCE_LO;

EPwm2Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm3Regs.TZCTL.bit.TZA = TZ_FORCE_LO;

EPwm3Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm4Regs.TZCTL.bit.TZA = TZ_FORCE_LO;

EPwm4Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm1Regs.TZFRC.bit.OST = 1;

EPwm2Regs.TZFRC.bit.OST = 1;

EPwm3Regs.TZFRC.bit.OST = 1;

EPwm4Regs.TZFRC.bit.OST = 1;

EPwm1Regs.GLDCFG.all = 0x07FF;

EPwm1Regs.GLDCTL.bit.GLDMODE = 6;

EPwm1Regs.GLDCTL.bit.OSHTMODE = 1;

EPwm1Regs.GLDCTL.bit.GLD = 1;

EPwm1Regs.EPWMXLINK.bit.GLDCTL2LINK = 0;

EPwm2Regs.GLDCFG.all = 0x07FF;

EPwm2Regs.GLDCTL.bit.GLDMODE = 6;

EPwm2Regs.GLDCTL.bit.OSHTMODE = 1;

EPwm2Regs.GLDCTL.bit.GLD = 1;

EPwm2Regs.EPWMXLINK.bit.GLDCTL2LINK = 0;

EPwm3Regs.GLDCFG.all = 0x07FF;

EPwm3Regs.GLDCTL.bit.GLDMODE = 6;

EPwm3Regs.GLDCTL.bit.OSHTMODE = 1;

EPwm3Regs.GLDCTL.bit.GLD = 1;

EPwm3Regs.EPWMXLINK.bit.GLDCTL2LINK = 0;

EPwm4Regs.GLDCFG.all = 0x07FF;

EPwm4Regs.GLDCTL.bit.GLDMODE = 6;

EPwm4Regs.GLDCTL.bit.OSHTMODE = 1;

EPwm4Regs.GLDCTL.bit.GLD = 1;

EPwm4Regs.EPWMXLINK.bit.GLDCTL2LINK = 0;

EDIS;

EPwm1Regs.TBPRD = EPWMPeriod;

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1; // TBCLK = SYSCLKOUT /(HSPCLKDIV ×CLKDIV)

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm1Regs.TBCTL.bit.PHSDIR = TB_UP;

EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm1Regs.TBCTL.bit.PHSEN = TB_ENABLE; //使能同步

EPwm1Regs.TBPHS.bit.TBPHS = 0;

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count updown

EPwm1Regs.EPWMSYNCINSEL.bit.SEL = SYNC_IN_SRC_DISABLE_ALL;

EPwm1Regs.EPWMSYNCOUTEN.bit.ZEROEN = SYNC_OUT_SRC_ENABLE;

EPwm2Regs.TBPRD = EPWMPeriod;

EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV1; // TBCLK = SYSCLKOUT /(HSPCLKDIV ×CLKDIV)

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm2Regs.TBCTL.bit.PHSDIR = TB_UP;

EPwm2Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm2Regs.TBPHS.bit.TBPHS = 2;

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count updown

EPwm2Regs.EPWMSYNCINSEL.bit.SEL = SYNC_IN_SRC_SYNCOUT_EPWM1;

EPwm3Regs.TBPRD = EPWMPeriod;

EPwm3Regs.TBCTL.bit.CLKDIV = TB_DIV1; // TBCLK = SYSCLKOUT /(HSPCLKDIV ×CLKDIV)

EPwm3Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm3Regs.TBCTL.bit.PHSDIR = TB_UP;

EPwm3Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm3Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm3Regs.TBPHS.bit.TBPHS = 3; //补偿10ns数字隔离器延迟

EPwm3Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count updown

EPwm3Regs.EPWMSYNCINSEL.bit.SEL = SYNC_IN_SRC_SYNCOUT_EPWM1;

EPwm4Regs.TBPRD = EPWMPeriod;

EPwm4Regs.TBCTL.bit.CLKDIV = TB_DIV1; // TBCLK = SYSCLKOUT /(HSPCLKDIV ×CLKDIV)

EPwm4Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm4Regs.TBCTL.bit.PHSDIR = TB_UP;

EPwm4Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm4Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm4Regs.TBPHS.bit.TBPHS = 3; //补偿10ns数字隔离器延迟

EPwm4Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count updown

EPwm4Regs.EPWMSYNCINSEL.bit.SEL = SYNC_IN_SRC_SYNCOUT_EPWM1;

EPwm5Regs.TBPRD = 1000;

EPwm5Regs.TBCTL.bit.CLKDIV = TB_DIV1; // TBCLK = SYSCLKOUT /(HSPCLKDIV ×CLKDIV)

EPwm5Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm5Regs.TBCTL.bit.PHSDIR = TB_UP;

EPwm5Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm5Regs.TBCTL.bit.PHSEN = TB_DISABLE;

// EPwm5Regs.TBPHS.bit.TBPHS = 2; //补偿10ns数字隔离器延迟

EPwm5Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count updown

EPwm5Regs.EPWMSYNCINSEL.bit.SEL = SYNC_IN_SRC_DISABLE_ALL;

//计数比较模块设定

EPwm1Regs.TBCTR = 0; //计数初值为0

EPwm1Regs.CMPA.bit.CMPA = EPWMPeriod_DIV2 - LeastTime_LLC;

EPwm1Regs.CMPB.bit.CMPB = EPWMPeriod_DIV2 + LeastTime_LLC;

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm2Regs.TBCTR = 0; //计数初值为0

EPwm2Regs.CMPA.bit.CMPA = EPWMPeriod_DIV2 - LeastTime_LLC;

EPwm2Regs.CMPB.bit.CMPB = EPWMPeriod_DIV2 + LeastTime_LLC;

EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm3Regs.TBCTR = 0; //计数初值为0

EPwm3Regs.CMPA.bit.CMPA = EPWMPeriod_DIV2 - LeastTime_LLC;

EPwm3Regs.CMPB.bit.CMPB = EPWMPeriod_DIV2 + LeastTime_LLC;

EPwm3Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm3Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

EPwm3Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm3Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm4Regs.TBCTR = 0; //计数初值为0

EPwm4Regs.CMPA.bit.CMPA = EPWMPeriod_DIV2 - LeastTime_LLC;

EPwm4Regs.CMPB.bit.CMPB = EPWMPeriod_DIV2 + LeastTime_LLC;

EPwm4Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm4Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

EPwm4Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm4Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm5Regs.TBCTR = 0; //计数初值为0

// EPwm5Regs.CMPA.bit.CMPA = 0;

// EPwm5Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

// EPwm5Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

// AQ模块设定

EPwm1Regs.AQCTLA.bit.CAU = AQ_SET;

EPwm1Regs.AQCTLA.bit.CBU = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.CBD = AQ_SET;

EPwm1Regs.AQCTLB.bit.CAD = AQ_CLEAR;

EPwm1Regs.AQCTLA.bit.ZRO = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.ZRO = AQ_CLEAR;

EPwm2Regs.AQCTLB.bit.CAU = AQ_SET;

EPwm2Regs.AQCTLB.bit.CBU = AQ_CLEAR;

EPwm2Regs.AQCTLA.bit.CBD = AQ_SET;

EPwm2Regs.AQCTLA.bit.CAD = AQ_CLEAR;

EPwm2Regs.AQCTLA.bit.ZRO = AQ_CLEAR;

EPwm2Regs.AQCTLB.bit.ZRO = AQ_CLEAR;

EPwm3Regs.AQCTLA.bit.CAU = AQ_SET;

EPwm3Regs.AQCTLA.bit.CBU = AQ_CLEAR;

EPwm3Regs.AQCTLB.bit.CBD = AQ_SET;

EPwm3Regs.AQCTLB.bit.CAD = AQ_CLEAR;

EPwm3Regs.AQCTLA.bit.ZRO = AQ_CLEAR;

EPwm3Regs.AQCTLB.bit.ZRO = AQ_CLEAR;

EPwm4Regs.AQCTLB.bit.CAU = AQ_SET;

EPwm4Regs.AQCTLB.bit.CBU = AQ_CLEAR;

EPwm4Regs.AQCTLA.bit.CBD = AQ_SET;

EPwm4Regs.AQCTLA.bit.CAD = AQ_CLEAR;

EPwm4Regs.AQCTLA.bit.ZRO = AQ_CLEAR;

EPwm4Regs.AQCTLB.bit.ZRO = AQ_CLEAR;

//DB死区模块设定

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_DISABLE;

EPwm2Regs.DBCTL.bit.OUT_MODE = DB_DISABLE;

EPwm3Regs.DBCTL.bit.OUT_MODE = DB_DISABLE;

EPwm4Regs.DBCTL.bit.OUT_MODE = DB_DISABLE;

EPwm1Regs.GLDCTL2.bit.GFRCLD = 1;

EPwm5Regs.ETSEL.bit.SOCAEN = 1; // 1 Enable the ADC Start of Conversion B (EPWMxSOCB) Pulse, Enable EPWMxSOCB pulse.

EPwm5Regs.ETSEL.bit.SOCASEL = ET_CTR_ZERO; //PRD 触发ADC_B

EPwm5Regs.ETPS.bit.SOCAPRD = ET_1ST;

// EPwm1Regs.ETSEL.bit.INTEN = 1; // 1 Enable the ADC Start of Conversion B (EPWMxSOCB) Pulse, Enable EPWMxSOCB pulse.

// EPwm1Regs.ETSEL.bit.INTSEL = ET_CTR_ZERO; //PRD 触发ADC_B

// EPwm1Regs.ETPS.bit.INTPRD = ET_1ST;

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 1;

EDIS;

}update ePWM parameters code:

void loadpwm()

{

F_SW = CC_PID.PIDU; //PI计算值

F_SW = __fmin(150,F_SW);

F_SW = __fmax(80,F_SW);

EPWMPeriod = 50000 / F_SW;

EPWMPeriod_DIV2 = EPWMPeriod / 2;

LLC_Hduty_EPWM = LLC_duty * EPWMPeriod_DIV2;

if( LLC_Hduty_EPWM > EPWMPeriod_DIV2 - 25 )

{

LLC_Hduty_EPWM = EPWMPeriod_DIV2 - 25;

}

EPWMPeriod = EPWM_Cal_SW / F_SW;

EPWMPeriod_DIV2 = EPWMPeriod / 2;

EPWMPeriod = EPWMPeriod_DIV2 * 2;

F_Int = 50;

T_Ctrl = 0.001f/F_Int;

EPwm3Regs.TBPRD = EPWMPeriod; //Period of TB = 10kHz

EPwm4Regs.TBPRD = EPWMPeriod; //Period of TB = 10kHz

EPwm3Regs.CMPA.bit.CMPA = EPWMPeriod_DIV2 - LLC_Hduty_EPWM;

EPwm3Regs.CMPB.bit.CMPB = EPWMPeriod_DIV2 + LLC_Hduty_EPWM;

EPwm4Regs.CMPA.bit.CMPA = EPWMPeriod_DIV2 - LLC_Hduty_EPWM;

EPwm4Regs.CMPB.bit.CMPB = EPWMPeriod_DIV2 + LLC_Hduty_EPWM;

EPwm1Regs.GLDCTL2.bit.OSHTLD = 1;

}• issue:

When the LLC adjusts the frequency downward from 85K to close to 80K, there is a chance that the drive signals of the upper and lower half-bridge MOS tubes will occasionally be high at the same time.

The MOS tube is short-circuited and the tube is burned out.

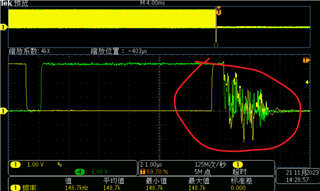

The waveform and frequency before shorted:

The following figure shows the waveform at the moment of short circuit (PI parameters are not adjusted well), output oscillation occurs: blue is the LLC input voltage, yellow is the LLC resonant inductor current, and green is the LLC output current.

This issue occurs at the every C2000 devices occasionally. The conditions that occur are that during the charging and starting process, the LLC output is loaded for a few seconds, the LLC input voltage drops, and then the LLC performs frequency modulation. The frequency is close to the lower limit frequency of about 80K, and a through short circuit may occur.

The customer generate Dead-Band time by using different compare value with different action. The DB module is bypassed.

The glitches on ePWM output pins make me confused:

--

Thanks & Regards

Hi Yale,

Could we move the thread to the customer's posted thread? I am going to close this thread for now and respond the the thread below.

I see another duplicate thread here: https://e2e.ti.com/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/1295694/tms320f280021-q1-epwm-for-llc-control-process-pwm-outputs-are-both-high-level-issue

Best,

Ryan Ma