Other Parts Discussed in Thread: C2000WARE

Dear Champs,

I am asking this for our customer.

The user is migrating codes from F280049C onto F280039C.

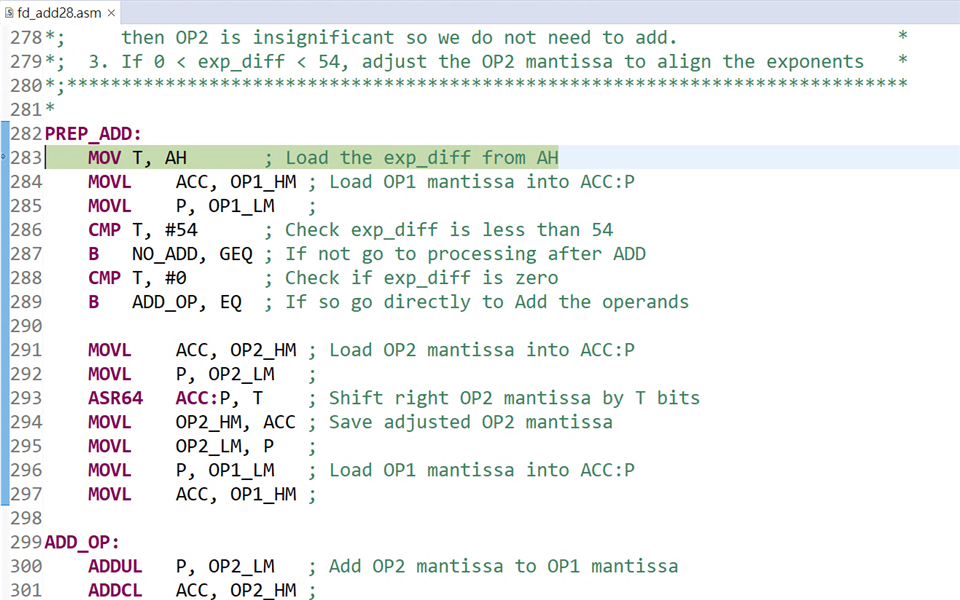

It weird that after ISRs are running (right after EINT;), the code is stuck in fd_add28.asm/fd_sub28.asm/fd_mpy28.asm..., which are all part of RTS library (rts2800_fpu32_eabi.lib).

Like below. Code is running and stuck in these files.

F280049 uses COFF but F280039C uses EABI in our migration.

Note that when I use stuck, it does not mean the code is in ESTOP.

Instead, I mean that the code is running in these files and could not go back to main().

But on F280049, it can run normally.

When we used only one ISR (ADCA1 ISR or Timer0 ISR) and traced them step-by-step, it seemed to work. But when we ran them both (ADCA1 ISR and Timer0 ISR), then this issue happened.

Would you please help us debug this?

Questions:

1. Why does the user's ISR code can go into these RTS library codes during runtime (after user's initialization and EINT;)?

2. Are these codes related to double type, which is viewed as 64-bit in EABI rather than 32-bit in COFF? We tried to check the user's code, there were a few long-double variables. But these should be done by compiler. It's very hard to imagine the code can be stuck there?

3. Do you have any suggestion for us to debug?