Part Number: LAUNCHXL-F28379D

Hello TI Community,

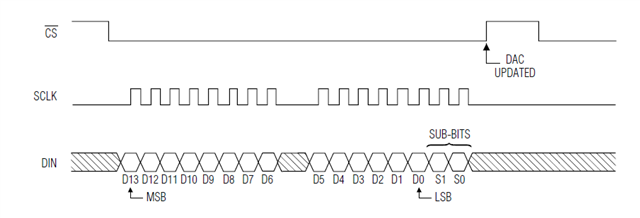

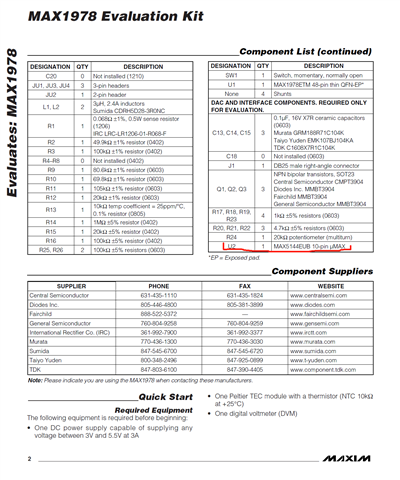

I am experiencing intermittent errors during SPI communication with a MAX1978 device. The communication works correctly for several cycles, sending and receiving the expected data (as shown by the initial correct 0x88 values in the waveform). However, occasionally the transmission is followed by errors where the expected data is not correctly received or sent (indicated by 'Error' in the waveform).

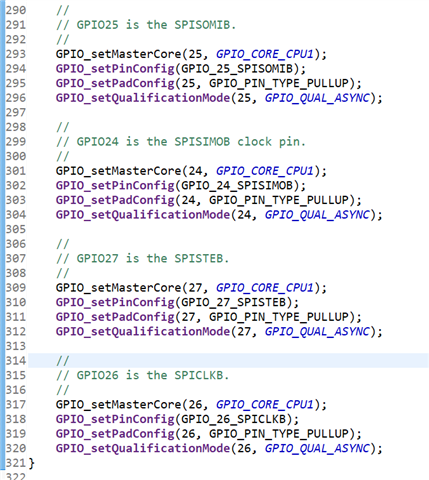

The errors are sporadic and do not follow a clear pattern. The waveform suggests that the issue may lie in the SPI configuration or signal integrity, but I've double-checked the settings, and they align with the device's requirements. The clock frequency, SPI mode, and bit order are configured according to the datasheet specifications, and the hardware connections have been verified.

Have any of you encountered similar issues or do you have insights into potential causes? Any suggestions for troubleshooting or specific areas to inspect would be greatly appreciated.

Thank you for your assistance.

Best regards,

Nero Dai

spi_ex3_external_loopback_fifo_interrupts.zipFull Code is here