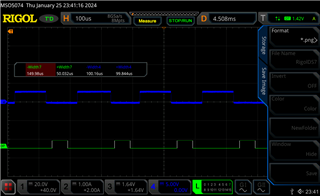

I'm running a simple test of a toggle signal. In blue i send the signal through a DAC, and in green im sending it through the ePWM 4B. im running the card at a frequency of 10kHz and the DAC work as expected with 100us width in the positive and negative section. But the ePWM signal have a negative width of 150us and positive width of 50us. I have already configurated the ePWM propoerly for an Up-Down mode, with shadow register, a load time at counter zero,

-----------------------control loop-------------------------------------------------------

c = !c;

write_DACB_pu(c);

write_ePWMxB(4,c);

---------------------functions---------------------------------------------------

void write_DACB_pu(float out)

{

if (out<0)

out = 0;

if (out>1)

out = 1;

if (Board_Type==1)

out=1-out;

DacbRegs.DACVALS.all = (unsigned int)(out*4095) ;

}

void write_ePWMxA(unsigned int pwm, float d)

{

unsigned int out =0;

if (d<0)

d=0;

if (d>1)

d=1;

if (pwm<13){

ePWMAx_duty_cycle[pwm-1] = d;

out = (unsigned int)(d*ePWMx_TMAX[pwm-1]);

if (pwm==1)

EPwm1Regs.CMPA.bit.CMPA = out; // adjust duty for output EPWM1A

if (pwm==2)

EPwm2Regs.CMPA.bit.CMPA = out; // adjust duty for output EPWM2A

if (pwm==3)

EPwm3Regs.CMPA.bit.CMPA = out; // adjust duty for output EPWM3A

if (pwm==4)

EPwm4Regs.CMPA.bit.CMPA = out; // adjust duty for output EPWM4A

if (pwm==5)

EPwm5Regs.CMPA.bit.CMPA = out; // adjust duty for output EPWM5A

if (pwm==6)

EPwm6Regs.CMPA.bit.CMPA = out; // adjust duty for output EPWM6A

if (pwm==7)

EPwm7Regs.CMPA.bit.CMPA = out; // adjust duty for output EPWM7A

if (pwm==8)

EPwm8Regs.CMPA.bit.CMPA = out; // adjust duty for output EPWM8A

if (pwm==9)

EPwm9Regs.CMPA.bit.CMPA = out; // adjust duty for output EPWM9A

if (pwm==10)

EPwm10Regs.CMPA.bit.CMPA = out; // adjust duty for output EPWM10A

if (pwm==11)

EPwm11Regs.CMPA.bit.CMPA = out; // adjust duty for output EPWM11A

if (pwm==12)

EPwm12Regs.CMPA.bit.CMPA = out; // adjust duty for output EPWM12A

}

}

---------------------------------Initialization---------------------------------------------

void init_ALL_ePWMs(void)

{

// enable PWMs

CpuSysRegs.PCLKCR2.bit.EPWM1=1;

CpuSysRegs.PCLKCR2.bit.EPWM2=1;

CpuSysRegs.PCLKCR2.bit.EPWM3=1;

CpuSysRegs.PCLKCR2.bit.EPWM4=1;

CpuSysRegs.PCLKCR2.bit.EPWM5=1;

CpuSysRegs.PCLKCR2.bit.EPWM6=1;

InitEPwmGpio();

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0;

EDIS;

InitEPwm1();

InitEPwm2();

InitEPwm3();

InitEPwm4();

InitEPwm5();

InitEPwm6();

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 1;

EDIS;

}

void InitEPwm4()

{

unsigned pwm = 4;

// Set Clock

EPwm4Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm4Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm4Regs.TBPRD = ePWMx_TMAX[pwm-1]; // Set timer period (Max Count)

EPwm4Regs.TBPHS.bit.TBPHS = ePWMx_PS[pwm-1]; // Phase Shift (initial counter value)

EPwm4Regs.TBCTR = 0x0000; // Clear counter

// Set Compare values

EPwm4Regs.CMPA.bit.CMPA = 0; // Set compare A value

EPwm4Regs.CMPB.bit.CMPB = 0; // Set Compare B value

// Setup counter mode

EPwm4Regs.TBCTL.bit.PHSDIR = readbit(ePWMx_PHSDIR,pwm-1); // Set Initial Count Direction

unsigned int pos = 2*(pwm-1);

unsigned int symm = readbit(ePWMx_SYMM,pos) + 2*readbit(ePWMx_SYMM,pos+1);

EPwm4Regs.TBCTL.bit.CTRMODE = symm; // Count up and down -- Symmetric PWM /\/\/

EPwm4Regs.TBCTL.bit.PHSEN = TB_ENABLE; // Enable phase loading

EPwm4Regs.TBCTL.bit.PRDLD = TB_SHADOW; // Upload duty-cycle in the next sampling

EPwm4Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // sync flow-through to sync EPWM5

// Setup shadowing

EPwm4Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm4Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

//EPwm4Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO_PRD; // (Double Update) Load on Zero and Period

EPwm4Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // modificado baldo

EPwm4Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

// PWM Logic

//************************

// EPWM4A Positive

EPwm4Regs.AQCTLA.bit.CAU = AQ_CLEAR; // set actions for EPWM4A

EPwm4Regs.AQCTLA.bit.CAD = AQ_SET;

// EPWM4B Positive

EPwm4Regs.AQCTLB.bit.CBU = AQ_CLEAR; // set actions for EPWM4B

EPwm4Regs.AQCTLB.bit.CBD = AQ_SET;

// EPWM4B Negative

//EPwm4Regs.AQCTLB.bit.CBU = AQ_SET; // set actions for EPWM4B

//EPwm4Regs.AQCTLB.bit.CBD = AQ_CLEAR;

// Timer Interrupt

EPwm4Regs.ETSEL.bit.INTSEL = ET_CTR_ZERO; // (single update) Select INT on Zero event

//EPwm4Regs.ETSEL.bit.INTSEL = ET_CTR_PRD; // (single update) Select INT on Period (Max count) event

//EPwm4Regs.ETSEL.bit.INTSEL = ET_CTR_PRDZERO; // (double update) Select INT on Zero and Period event

EPwm4Regs.ETSEL.bit.INTEN = 1; // Enable INT

EPwm4Regs.ETPS.bit.INTPRD = ET_1ST; // Generate INT on 1st event

//dead-time

if (readbit(ePWMx_COMP,pwm-1) == 1)

{

EPwm4Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // enable Dead-band module

EPwm4Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

unsigned int temp_DB = (unsigned int)(DB_Gain_ns*ePWMx_DB[pwm-1]);

EPwm4Regs.DBFED.bit.DBFED = temp_DB;

EPwm4Regs.DBRED.bit.DBRED = temp_DB;

}

else

EPwm4Regs.DBCTL.bit.OUT_MODE = DB_DISABLE;

}