Other Parts Discussed in Thread: SYSCONFIG

Hi,

I have perfectly the same issue, but it is not clear for me how to fix it.

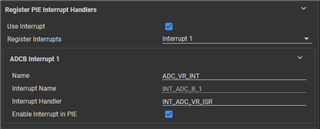

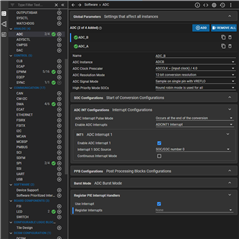

I am using SysConfig in CPU1 to configure ADCA and ADCB, ePWM1/2/6/7/8/ and ADCA/B Interrupts, but I need to manage ADCA interrupt in CPU1 and ADCB interrupt in CPU2. The same ISR is entered if everything is in CPU1, it is not entered if it is in CPU2.

This is my code in CPU2 main and the related ISR.

...

//

// Initialize PIE and clear PIE registers. Disables CPU interrupts.

//

Interrupt_initModule();

//

// Initialize the PIE vector table with pointers to the shell Interrupt

// Service Routines (ISR).

//

Interrupt_initVectorTable();

// Interrupt Settings for INT_ADCB1

Interrupt_register(INT_ADCB1, &INT_ADC_VR_ISR);

Interrupt_enable(INT_ADCB1);

...

void INT_ADC_VR_ISR(void){

//

// Clear the interrupt flag

ADC_clearInterruptStatus(ADC_B_BASE, ADC_INT_NUMBER1);

//

// Check if overflow has occurred

if(true == ADC_getInterruptOverflowStatus(ADC_B_BASE, ADC_INT_NUMBER1))

{

ADC_clearInterruptOverflowStatus(ADC_B_BASE, ADC_INT_NUMBER1);

ADC_clearInterruptStatus(ADC_B_BASE, ADC_INT_NUMBER1);

}

//

// Acknowledge the interrupt

Interrupt_clearACKGroup(INTERRUPT_ACK_GROUP1);

}

What am I missing tin order to trigger correctly the interrupt in CPU2?

Thanks ,

Fabio