Other Parts Discussed in Thread: UNIFLASH

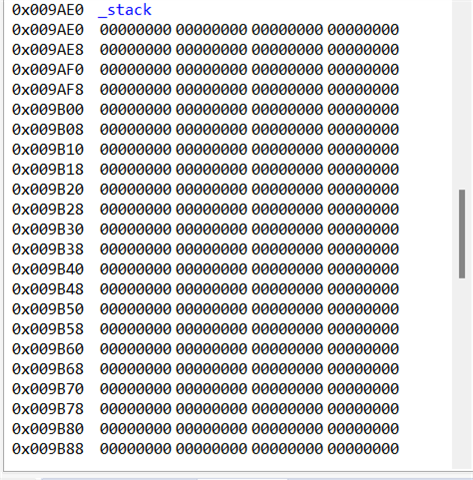

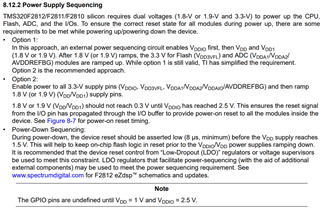

We have used the TMSF2812 for over 15 years and have more than 20 different applications that are based on the 2812. Starting approximately 2 years ago, we have started seeing a problem where on some boards, but not all, systems will lock up. Investigating on a test setup, I can see through JTAG that an illegal ISR is triggered and when that occurs, I can see internal flash reports all 0 and the security passwords show 0. Before the lockup, the security passwords are correct. It appears that they are not really gone. Simply resetting the firmware through JTAG, the passwords are back. The time that it takes to lockup varies quite a bit. Heating the board makes it more likely to occur. Again, this problem has appeared across multiple applications. But we also see that using one application on multiple boards shows that the problem only occurs on a subset of those boards. We have been unable to isolate this problem to hardware or software so far, although hardware seems likely.

I would appreciate any suggestions on what we should look at based on these observations.

Thank you very much!