Part Number: TMS320F28379D

Other Parts Discussed in Thread: C2000WARE

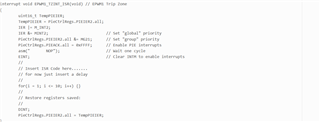

IER |= 0x003; // Set global priority by adjusting IER IER &= 0x003; (enabling EPWM interrupt)

the ADC ISR gets pushed to stack and the EPWM ISR will execute now. After the EPWM ISR gets executed ADC ISR will continue now. Is my understanding correct?

Thanks in advance!