Hi Champ,

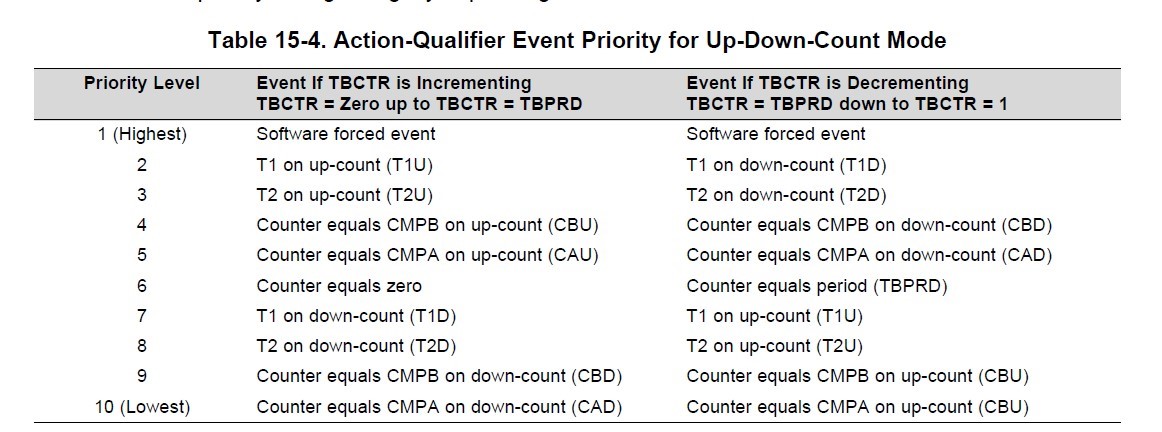

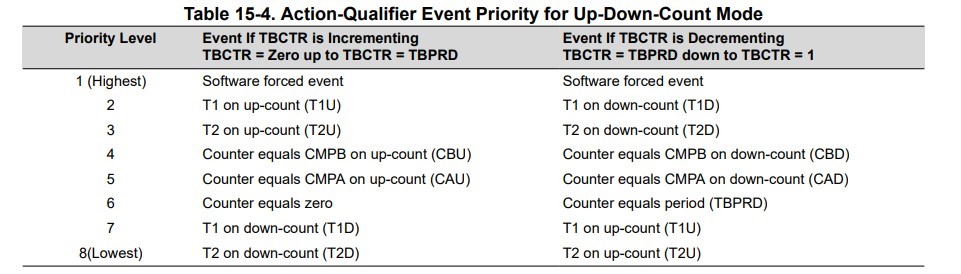

I want to confirm with you the detail about PWM Action-Qualifier Event Priority,.

for example, if level 4 and level 6 events happen at the same time,

How is the actual action on PWM output?

1. Just level 4 event will output on PWM PIN?

2. level 4 event action first then level 6 event will action that means final action on PWM output will be level 6 event?

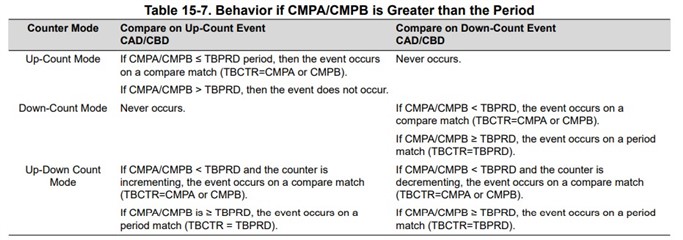

Another questions:

for example,

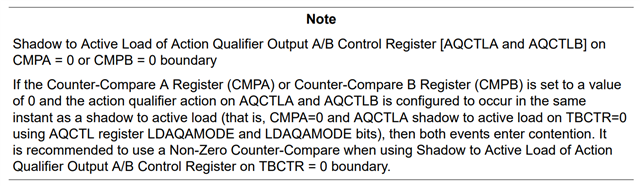

1. if CMPB is 3000, TBPRD is 3000, CBU will clear PWM, CBD will set PWM, TBPRD will clear PWM, which event will take action on CTR=TBPRD point ? CBD ,TBPRD, CBU?

2. if CMPB is 0, TBPRD is 3000, CBU will clear PWM, CBD will set PWM, Zero will set PWM, which event will take action on CTR=0 point ? CBD ,Zero, CBU?