Part Number: TMS320F28379D

Hey folks,

I generated intel hex file for my application on 28379d device.

the section paragraph in my linker command file looks like this:

SECTIONS

{

/* Allocate program areas: */

.cinit : > FLASHB | FLASHC PAGE = 0, ALIGN(8)

.text : >> FLASHB | FLASHC | FLASHD | FLASHE PAGE = 0, ALIGN(8)

codestart : > APP_START PAGE = 0, ALIGN(8)

/* Allocate uninitalized data sections: */

.stack : > RAMM1 PAGE = 1

.switch : > FLASHB PAGE = 0, ALIGN(8)

.reset : > RESET, PAGE = 0, TYPE = DSECT /* not used, */

#if defined(__TI_EABI__)

.init_array : > FLASHB | FLASHC, PAGE = 0, ALIGN(8)

.bss : > RAMLS4LS5, PAGE = 1

.bss:output : > RAMLS4LS5, PAGE = 1

.bss:cio : > RAMLS4LS5, PAGE = 1

.data : > RAMLS4LS5, PAGE = 1

.sysmem : > RAMLS4LS5, PAGE = 1

/* Initalized sections go in Flash */

.const : > FLASHF, PAGE = 0, ALIGN(8)

#else

.pinit : > FLASHB, PAGE = 0, ALIGN(8)

.ebss : >> RAMLS4LS5 | RAMGS0 | RAMGS1, PAGE = 1

.esysmem : > RAMLS4LS5, PAGE = 1

.cio : > RAMLS4LS5, PAGE = 1

/* Initalized sections go in Flash */

.econst : >> FLASHF PAGE = 0, ALIGN(8)

#endif

// Filter_RegsFile : > RAMGS0, PAGE = 1

// SHARERAMGS0 : > RAMGS0, PAGE = 1

// SHARERAMGS1 : > RAMGS1, PAGE = 1

// SHARERAMGS2 : > RAMGS2, PAGE = 1

// ramgs0 : > RAMGS0, PAGE = 1

// ramgs1 : > RAMGS1, PAGE = 1

#ifdef __TI_COMPILER_VERSION__

#if __TI_COMPILER_VERSION__ >= 15009000

#if defined(__TI_EABI__)

GROUP

{

.TI.ramfunc

{

-l sfra_f32_tmu_eabi.lib

}

ramfuncs

isrcodefuncs

} LOAD = FLASHD,

RUN = RAMLS0LS1LS2LS3,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

PAGE = 0, ALIGN(8)

#else

.TI.ramfunc : {} LOAD = FLASHD,

RUN = RAMLS0LS1LS2LS3,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

PAGE = 0, ALIGN(8)

#endif

#else

ramfuncs : LOAD = FLASHD,

RUN = RAMLS0,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

PAGE = 0, ALIGN(8)

#endif

#endif

...

}

As can be seen, ALIGN(8) is used for every appearance of allocations in FLASH.

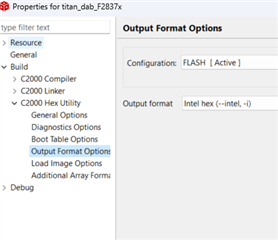

And I used the hex utility to let CCS12 auto generate the hex output, use intel format

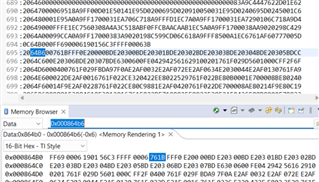

but when I check the intel hex files generated, for example my app.hex, it shows like:

:020000040008F2 (first line, significant of starting address is 0x0008)

...

:2064B60076FFE200E200E201E202E203E204E205E206E207E606FE2956290276025600FFE2

so, according to the intel format definision, it indicates starting at adress of 000864B6, the hex image data is 76.... etc.

The address 000864B6 is in the FLASH section D. Apparently this start address is not aligned to 128bit boundary. But I assure that the FLASHD is set to be ALIGN(8) everywhere in the .cmd file.

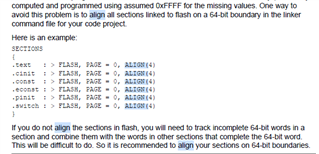

According to the spnu629a documentation,

My understanding is with the ALIGN(4) or (8), the content in the flash section should be aligned to 64-bit or 128-bit segments, respectively, which is to say, with ALIGN(8), the address of the generated image hex should always start at xxx8 or xxx0 in the flash memory, but I doubt my understanding based on this observation.

Could you provide some advice on what I am missing? or is there a way to force the hex file generated to be always starting at xxx8 / xxx0 which is 128 bit aligned, for the simpleness of flash operation.

Appreciate for the help.

Regards,

Wei