Tool/software:

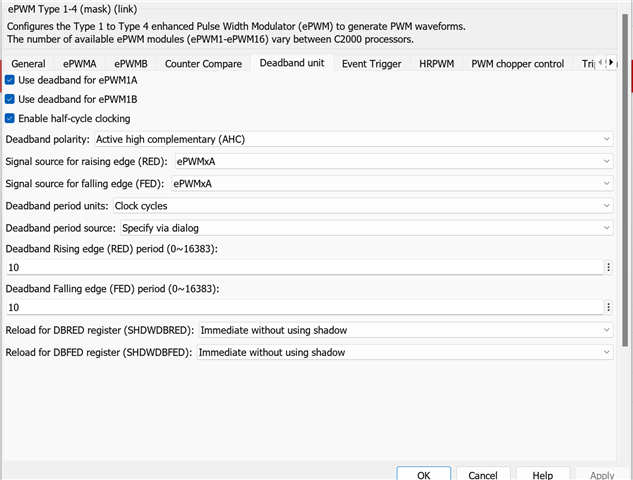

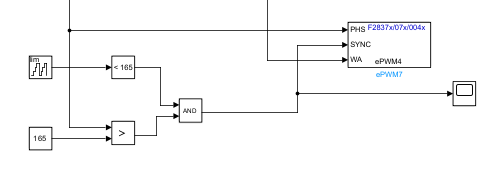

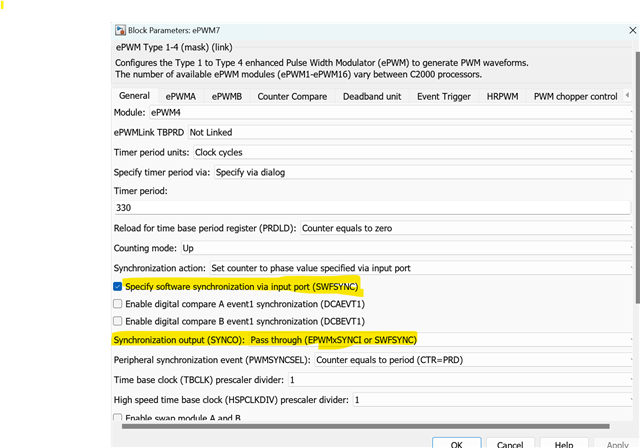

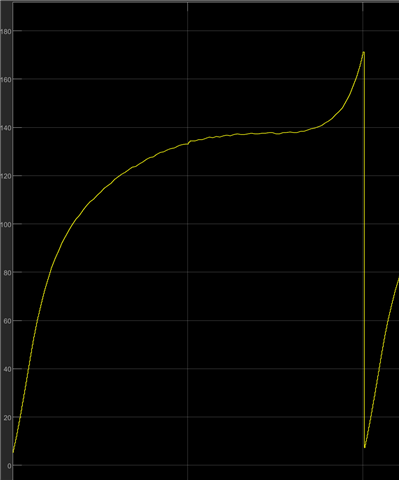

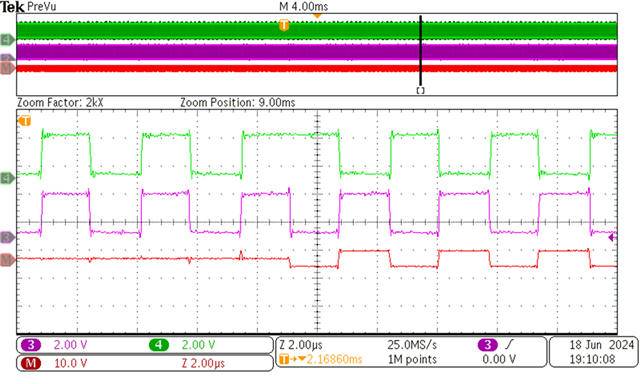

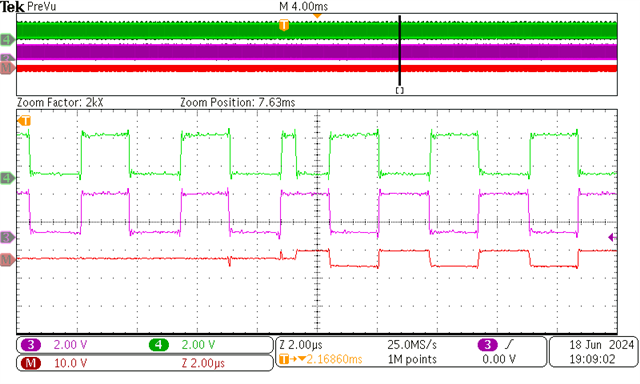

Hello I am doing dc-ac power conversion testing using this microcontroller. I am having issues with missing pulses. I am using four epwm outputs to control phase shift of four half-bridge legs. I do have a sharp transition in the phase shift values (from say -90 degree to 90 degree) near the zero crossing - which is where I am having issue. I compute the phase shift values using matlab and then use a lookup table to map them with the corresponding grid voltage.

How can I resolve this issue?

Thank you in advance.