- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hello,

I'm looking for a solution to my problem.

I am developing embedded software using CCS12.6 with LAUNCHXL-F28379D hardware.

The sample code I used is "gpio_ex2_toggle" and the CPU selection is CPU1 only.

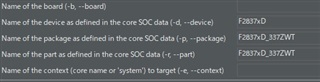

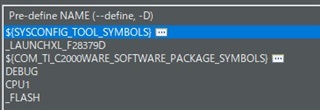

To match the hardware configuration of the LAUNCHXL-F28379D, change the package and part options in the Sysconfig->Basic option of the project properties to "F2837xD_337ZWT" and the Predefined symbol in C2000_Compiler Predefined symbol "_LAUNCHXL-F28379D" is added in C2000_Compiler.

In the early stages of software development, we were able to activate the CPU1_FLASH configuration and verify that we could write code to the internal FLASH ROM, that we could execute the expected operation, and that the software would work again even after the hardware reset button was pressed.

We have since switched the configuration to CPU1_RAM and added software functions. When the configuration is CPU1_RAM, the software runs as per the functions incorporated. However, when the configuration is switched to CPU1_FLASH, the software does not work.

In the software under development, the LED is turned on during the initialization of the peripheral in the main() routine.

After executing the build with the CPU1_FLASH configuration and writing to FLASH_ROM, when the hardware reset button is pressed, the LED lights up, so I assume that the software is able to execute until the middle of the main() routine.

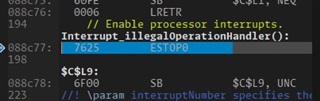

After that, the software stops at the breakpoint shown in the figure below, and disassembling the software shows that it stops at ESTOP0.

Are there any possible causes or countermeasures?

Hello,

Just to verify:

You haven't edited either of the linker cmd files (2837xD_RAM_lnk_cpu1.cmd and 2837xD_FLASH_lnk_cpu1.cmd), correct?

You are switching between build configurations using Build Configurations >> Set Active, correct?

Can you look at the .map file after doing the flash build to verify that all the program symbols are correctly located in an area of flash memory?

Best Regards,

Delaney

Ms. Delaney,

Thank you for your prompt reply.

We needed to place a large memory size when adding functionality to the software. In doing so, the message shown below was displayed, so we took action based on another article in this forum.

Therefore, the linker file has been edited for both RAM and FLASH. The contents of the linker files for RAM and FLASH are attached.

<2837xD_FLASH_lnk_cpu1.cmd>

MEMORY

{

PAGE 0 : /* Program Memory */

/* Memory (RAM/FLASH) blocks can be moved to PAGE1 for data allocation */

/* BEGIN is used for the "boot to Flash" bootloader mode */

BEGIN : origin = 0x080000, length = 0x000002

RAMM0 : origin = 0x000123, length = 0x0002DD

RAMD0 : origin = 0x00B000, length = 0x000800

RAMLS0 : origin = 0x008000, length = 0x000800

RAMLS1 : origin = 0x008800, length = 0x000800

RAMLS2 : origin = 0x009000, length = 0x000800

RAMLS3 : origin = 0x009800, length = 0x000800

RAMLS4 : origin = 0x00A000, length = 0x000800

RAMGS14 : origin = 0x01A000, length = 0x001000 /* Only Available on F28379D, F28377D, F28375D devices. Remove line on other devices. */

RAMGS15 : origin = 0x01B000, length = 0x000FF8 /* Only Available on F28379D, F28377D, F28375D devices. Remove line on other devices. */

// RAMGS15_RSVD : origin = 0x01BFF8, length = 0x000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

RESET : origin = 0x3FFFC0, length = 0x000002

/* Flash sectors */

FLASHA : origin = 0x080002, length = 0x001FFE /* on-chip Flash */

FLASHB : origin = 0x082000, length = 0x002000 /* on-chip Flash */

FLASHC : origin = 0x084000, length = 0x002000 /* on-chip Flash */

FLASHD : origin = 0x086000, length = 0x002000 /* on-chip Flash */

FLASHE : origin = 0x088000, length = 0x008000 /* on-chip Flash */

FLASHF : origin = 0x090000, length = 0x008000 /* on-chip Flash */

FLASHG : origin = 0x098000, length = 0x008000 /* on-chip Flash */

FLASHH : origin = 0x0A0000, length = 0x008000 /* on-chip Flash */

FLASHI : origin = 0x0A8000, length = 0x008000 /* on-chip Flash */

FLASHJ : origin = 0x0B0000, length = 0x008000 /* on-chip Flash */

FLASHK : origin = 0x0B8000, length = 0x002000 /* on-chip Flash */

FLASHL : origin = 0x0BA000, length = 0x002000 /* on-chip Flash */

FLASHM : origin = 0x0BC000, length = 0x002000 /* on-chip Flash */

FLASHN : origin = 0x0BE000, length = 0x001FF0 /* on-chip Flash */

// FLASHN_RSVD : origin = 0x0BFFF0, length = 0x000010 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

PAGE 1 : /* Data Memory */

/* Memory (RAM/FLASH) blocks can be moved to PAGE0 for program allocation */

BOOT_RSVD : origin = 0x000002, length = 0x000121 /* Part of M0, BOOT rom will use this for stack */

RAMM1 : origin = 0x000400, length = 0x0003F8 /* on-chip RAM block M1 */

// RAMM1_RSVD : origin = 0x0007F8, length = 0x000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

RAMD1 : origin = 0x00B800, length = 0x000800

RAMLS5 : origin = 0x00A800, length = 0x000800

RAMGS0 : origin = 0x00C000, length = 0x001000

RAMGS1 : origin = 0x00D000, length = 0x001000

RAMGS2 : origin = 0x00E000, length = 0x001000

RAMGS3 : origin = 0x00F000, length = 0x001000

RAMGS4 : origin = 0x010000, length = 0x001000

RAMGS5 : origin = 0x011000, length = 0x001000

RAMGS6 : origin = 0x012000, length = 0x001000

RAMGS7 : origin = 0x013000, length = 0x001000

RAMGS8 : origin = 0x014000, length = 0x001000

RAMGS9 : origin = 0x015000, length = 0x001000

RAMGS10 : origin = 0x016000, length = 0x001000

// RAMGS11 : origin = 0x017000, length = 0x000FF8 /* Uncomment for F28374D, F28376D devices */

// RAMGS11_RSVD : origin = 0x017FF8, length = 0x000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

RAMGS11 : origin = 0x017000, length = 0x001000 /* Only Available on F28379D, F28377D, F28375D devices. Remove line on other devices. */

RAMGS12 : origin = 0x018000, length = 0x001000 /* Only Available on F28379D, F28377D, F28375D devices. Remove line on other devices. */

RAMGS13 : origin = 0x019000, length = 0x001000 /* Only Available on F28379D, F28377D, F28375D devices. Remove line on other devices. */

CPU2TOCPU1RAM : origin = 0x03F800, length = 0x000400

CPU1TOCPU2RAM : origin = 0x03FC00, length = 0x000400

}

SECTIONS

{

/* Allocate program areas: */

.cinit : > FLASHB PAGE = 0, ALIGN(8)

/* .cinit : > FLASHA PAGE = 0, ALIGN(8) */

.text : >> FLASHC | FLASHD | FLASHE PAGE = 0, ALIGN(8)

codestart : > BEGIN PAGE = 0, ALIGN(8)

/* Allocate uninitalized data sections: */

.stack : > RAMM1 PAGE = 1

.switch : > FLASHB PAGE = 0, ALIGN(8)

.reset : > RESET, PAGE = 0, TYPE = DSECT /* not used, */

#if defined(__TI_EABI__)

.init_array : > FLASHB, PAGE = 0, ALIGN(8)

/* .bss : > RAMLS5, PAGE = 1 */

.bss:output : > RAMLS3, PAGE = 0

.bss:cio : > RAMLS5, PAGE = 1

.bss : >> RAMGS10 |RAMGS11 |RAMGS12 | RAMGS13, PAGE = 1

/* .bss:output : > RAMLS0 | RAMLS1 | RAMLS2 | RAMLS3 |RAMLS4, PAGE = 0 */

/* .bss:cio : > RAMLS0 | RAMLS1 | RAMLS2 | RAMLS3 |RAMLS4, PAGE = 0 */

.data : > RAMLS5, PAGE = 1

.sysmem : > RAMLS5, PAGE = 1

/* Initalized sections go in Flash */

.const : > FLASHF, PAGE = 0, ALIGN(8)

#else

.pinit : > FLASHB, PAGE = 0, ALIGN(8)

.ebss : >> RAMLS5 | RAMGS0 | RAMGS1, PAGE = 1

.esysmem : > RAMLS5, PAGE = 1

.cio : > RAMLS5, PAGE = 1

/* Initalized sections go in Flash */

.econst : >> FLASHF PAGE = 0, ALIGN(8)

#endif

Filter_RegsFile : > RAMGS0, PAGE = 1

SHARERAMGS0 : > RAMGS0, PAGE = 1

SHARERAMGS1 : > RAMGS1, PAGE = 1

SHARERAMGS2 : > RAMGS2, PAGE = 1

ramgs0 : > RAMGS0, PAGE = 1

ramgs1 : > RAMGS1, PAGE = 1

#ifdef __TI_COMPILER_VERSION__

#if __TI_COMPILER_VERSION__ >= 15009000

#if defined(__TI_EABI__)

.TI.ramfunc : {} LOAD = FLASHD,

RUN = RAMLS0,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

PAGE = 0, ALIGN(8)

#else

.TI.ramfunc : {} LOAD = FLASHD,

RUN = RAMLS0,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

PAGE = 0, ALIGN(8)

#endif

#else

ramfuncs : LOAD = FLASHD,

RUN = RAMLS0,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

PAGE = 0, ALIGN(8)

#endif

#endif

/* The following section definitions are required when using the IPC API Drivers */

GROUP : > CPU1TOCPU2RAM, PAGE = 1

{

PUTBUFFER

PUTWRITEIDX

GETREADIDX

}

GROUP : > CPU2TOCPU1RAM, PAGE = 1

{

GETBUFFER : TYPE = DSECT

GETWRITEIDX : TYPE = DSECT

PUTREADIDX : TYPE = DSECT

}

/* The following section definition are for SDFM examples */

Filter1_RegsFile : > RAMGS1, PAGE = 1, fill=0x1111

Filter2_RegsFile : > RAMGS2, PAGE = 1, fill=0x2222

Filter3_RegsFile : > RAMGS3, PAGE = 1, fill=0x3333

Filter4_RegsFile : > RAMGS4, PAGE = 1, fill=0x4444

Difference_RegsFile : >RAMGS5, PAGE = 1, fill=0x3333

/* Allocate IQ math areas: */

IQmath : > RAMLS1, PAGE = 0 /* Math Code */

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

<2837xD_RAM_lnk_cpu1.cmd>

MEMORY

{

PAGE 0 :

/* BEGIN is used for the "boot to SARAM" bootloader mode */

BEGIN : origin = 0x000000, length = 0x000002

RAMM0 : origin = 0x000123, length = 0x0002DD

RAMD0 : origin = 0x00B000, length = 0x000800

RAMLS0 : origin = 0x008000, length = 0x000800

RAMLS1 : origin = 0x008800, length = 0x000800

RAMLS2 : origin = 0x009000, length = 0x000800

RAMLS3 : origin = 0x009800, length = 0x000800

RAMLS4 : origin = 0x00A000, length = 0x000800

RESET : origin = 0x3FFFC0, length = 0x000002

/* Flash sectors */

FLASHA : origin = 0x080002, length = 0x001FFE /* on-chip Flash */

FLASHB : origin = 0x082000, length = 0x002000 /* on-chip Flash */

FLASHC : origin = 0x084000, length = 0x002000 /* on-chip Flash */

FLASHD : origin = 0x086000, length = 0x002000 /* on-chip Flash */

FLASHE : origin = 0x088000, length = 0x008000 /* on-chip Flash */

FLASHF : origin = 0x090000, length = 0x008000 /* on-chip Flash */

FLASHG : origin = 0x098000, length = 0x008000 /* on-chip Flash */

FLASHH : origin = 0x0A0000, length = 0x008000 /* on-chip Flash */

FLASHI : origin = 0x0A8000, length = 0x008000 /* on-chip Flash */

FLASHJ : origin = 0x0B0000, length = 0x008000 /* on-chip Flash */

FLASHK : origin = 0x0B8000, length = 0x002000 /* on-chip Flash */

FLASHL : origin = 0x0BA000, length = 0x002000 /* on-chip Flash */

FLASHM : origin = 0x0BC000, length = 0x002000 /* on-chip Flash */

FLASHN : origin = 0x0BE000, length = 0x001FF0 /* on-chip Flash */

// FLASHN_RSVD : origin = 0x0BFFF0, length = 0x000010 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

PAGE 1 :

BOOT_RSVD : origin = 0x000002, length = 0x000121 /* Part of M0, BOOT rom will use this for stack */

RAMM1 : origin = 0x000400, length = 0x0003F8 /* on-chip RAM block M1 */

// RAMM1_RSVD : origin = 0x0007F8, length = 0x000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

RAMD1 : origin = 0x00B800, length = 0x000800

RAMLS5 : origin = 0x00A800, length = 0x000800

RAMGS0 : origin = 0x00C000, length = 0x001000

RAMGS1 : origin = 0x00D000, length = 0x001000

RAMGS2 : origin = 0x00E000, length = 0x001000

RAMGS3 : origin = 0x00F000, length = 0x001000

RAMGS4 : origin = 0x010000, length = 0x001000

RAMGS5 : origin = 0x011000, length = 0x001000

RAMGS6 : origin = 0x012000, length = 0x004000

/* RAMGS7 : origin = 0x013000, length = 0x001000 */

/* RAMGS8 : origin = 0x014000, length = 0x001000 */

/* RAMGS9 : origin = 0x015000, length = 0x001000 */

RAMGS10 : origin = 0x016000, length = 0x001000

// RAMGS11 : origin = 0x017000, length = 0x000FF8 /* Uncomment for F28374D, F28376D devices */

// RAMGS11_RSVD : origin = 0x017FF8, length = 0x000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

RAMGS11 : origin = 0x017000, length = 0x001000 /* Only Available on F28379D, F28377D, F28375D devices. Remove line on other devices. */

RAMGS12 : origin = 0x018000, length = 0x001000 /* Only Available on F28379D, F28377D, F28375D devices. Remove line on other devices. */

RAMGS13 : origin = 0x019000, length = 0x001000 /* Only Available on F28379D, F28377D, F28375D devices. Remove line on other devices. */

RAMGS14 : origin = 0x01A000, length = 0x001000 /* Only Available on F28379D, F28377D, F28375D devices. Remove line on other devices. */

RAMGS15 : origin = 0x01B000, length = 0x000FF8 /* Only Available on F28379D, F28377D, F28375D devices. Remove line on other devices. */

// RAMGS15_RSVD : origin = 0x01BFF8, length = 0x000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

/* Only on F28379D, F28377D, F28375D devices. Remove line on other devices. */

CPU2TOCPU1RAM : origin = 0x03F800, length = 0x000400

CPU1TOCPU2RAM : origin = 0x03FC00, length = 0x000400

CANA_MSG_RAM : origin = 0x049000, length = 0x000800

CANB_MSG_RAM : origin = 0x04B000, length = 0x000800

}

SECTIONS

{

codestart : > BEGIN, PAGE = 0

.text : >> RAMD1 | RAMGS0 | RAMGS1 | RAMGS2 | RAMGS3 | RAMGS4, PAGE = 1

/* .cinit : > RAMGS5 | RAMGS6 | RAMGS7 | RAMGS8 | RAMGS9 | RAMGS11, PAGE = 1*/

.cinit : > RAMGS5, PAGE = 1

.switch : > RAMM0, PAGE = 0

.reset : > RESET, PAGE = 0, TYPE = DSECT /* not used, */

.stack : > RAMM1, PAGE = 1

#if defined(__TI_EABI__)

/* .bss : > RAMGS10 | RAMGS11 | RAMGS12 | RAMGS13 | RAMGS14 | RAMGS15, PAGE = 1*/

.bss : >> RAMGS12 | RAMGS13 | RAMGS14 | RAMGS15, PAGE = 1

.bss:output : > RAMLS0 | RAMLS1 | RAMLS2 | RAMLS3 |RAMLS4, PAGE = 0

.init_array : > RAMM0, PAGE = 0

/* .const : >> RAMGS10 | RAMGS11 | RAMGS12, PAGE = 1*/

/* .const : >> RAMGS6 | RAMGS7 | RAMGS8 | RAMGS9 | RAMGS10 | RAMGS11, PAGE = 1 */

.const : >> RAMGS6, PAGE = 1

.data : >> RAMGS10 | RAMGS11 | RAMGS12 | RAMGS13 | RAMGS14 | RAMGS15, PAGE = 1

.sysmem : > RAMGS10, PAGE = 1

#else

.pinit : > RAMM0, PAGE = 0

.ebss : > RAMLS5, PAGE = 1

.econst : > RAMLS5, PAGE = 1

.esysmem : > RAMLS5, PAGE = 1

#endif

Filter_RegsFile : > RAMGS0, PAGE = 1

ramgs0 : > RAMGS0, PAGE = 1

ramgs1 : > RAMGS1, PAGE = 1

#ifdef __TI_COMPILER_VERSION__

#if __TI_COMPILER_VERSION__ >= 15009000

.TI.ramfunc : {} > RAMM0, PAGE = 0

#else

ramfuncs : > RAMM0 PAGE = 0

#endif

#endif

/* The following section definitions are required when using the IPC API Drivers */

GROUP : > CPU1TOCPU2RAM, PAGE = 1

{

PUTBUFFER

PUTWRITEIDX

GETREADIDX

}

GROUP : > CPU2TOCPU1RAM, PAGE = 1

{

GETBUFFER : TYPE = DSECT

GETWRITEIDX : TYPE = DSECT

PUTREADIDX : TYPE = DSECT

}

/* The following section definition are for SDFM examples */

Filter1_RegsFile : > RAMGS1, PAGE = 1, fill=0x1111

Filter2_RegsFile : > RAMGS2, PAGE = 1, fill=0x2222

Filter3_RegsFile : > RAMGS3, PAGE = 1, fill=0x3333

Filter4_RegsFile : > RAMGS4, PAGE = 1, fill=0x4444

Difference_RegsFile : >RAMGS5, PAGE = 1, fill=0x3333

/* Allocate IQ math areas: */

IQmath : > RAMLS0, PAGE = 0 /* Math Code */

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/We will check if all the other program symbols you mentioned are placed in the Flash memory area and will get back to you.

Hi Teruhiko,

I see, sounds good. Just to verify, is all that you changed in the linker cmd files the .text allocation?

Best Regards,

Delaney

Ms. Delaney,

Thank you for your quick response.

I am contacting you regarding changes to the Linker file.

First, here are the changes to the FlashROM version of the Linker File.

The left column is the modified version and the right column is the original.

Initialized global variable area ".cinit" is now independent from the executable code area because an error occurred when sharing it with the executable code area.

The global variable area ".bss" has also been extended.

The IQmath Library is now also used, so I was added it to the "SECTION" based on the sample code.

The next change is to the RAM version of the Linker File.

As mentioned above, to accommodate the larger size memory allocation, the area size of RAMGS6 was set to 4000h and RAMGS7 - RAMGS9 were commented out.

Because of the larger code size, the allocation of the ".text" area was changed. Allocation of ".bss", ".const", and ".data" areas was also changed.

I have noticed so far, should IQMath.lib be placed in the FlashROM area?

I don't have much experience with embedded software. Is there a manual on how to set up the linker file?

Ms.Delaney,.

I have checked the program symbols in the FlashROM version of the map file. As a result, all program symbols are located in the FlashROM area.

I think that the initialized global variables are placed in the “.data” area, so I don't see a problem with them being placed in the RAM area.

----------

I was searching the forum for IQmath.lib placement in linker file. I came across the following article as a result.

In this article, the linker file for FlashROM is “(Ex: XXX_FLASH_lnk_cpu1.cmd at C2000Ware_x_xx_xx_xx_xx_device_support\XXX\common\cmd)”I found that it is stored in. Browsing this folder, I found a Linker file (2837xD_FLASH_IQMATH_lnk_cpu1.cmd) that seems to be related to IQmath.Lib. This file explicitly placed IQMath in the FLASH area, so I modified my linker file in the same way, and now my software can boot from FlashROM.

/* Allocate IQ math areas: */ IQmath : > FLASHB, PAGE = 0, ALIGN(8) /* Math Code */ IQmathTables : > FLASHC, PAGE = 0, ALIGN(8)

Is it correct in assuming that the above is what was wrong in my linker file?

Hi Teruhiko,

I will look into this and get back to you.

Best Regards,

Delaney

Hi Teruhiko,

Yes, I believe that was your issue. Generally, if doing a flash build you always want to use one of the flash linker cmd files, and if using a library too, you should use the flash version of that library's linker cmd file (as you have mentioned). Here are some additional resources that may be helpful as well:

Linked here is a guide about linker cmd files that should be helpful to look at.

Please see the 3.6. Accessing IQmath Functions in the Boot ROM section of the IQMath user guide (linked here) for more information about using the IQMath library.

Best Regards,

Delaney

Ms. Delaney,

Thank you for your respons. Thanks to your help, my software problem can be resolved. Too much thanks!!