Tool/software:

Dear Team,

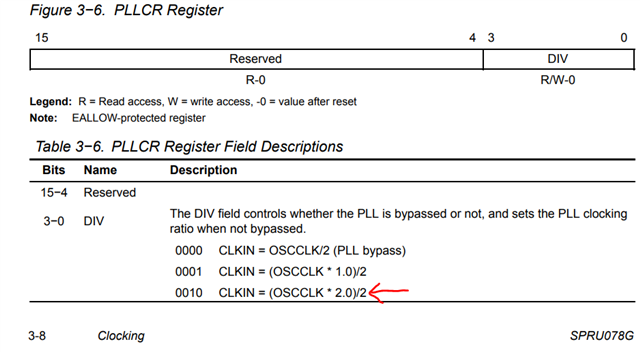

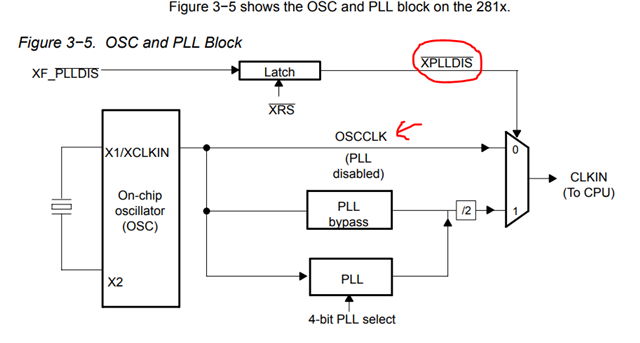

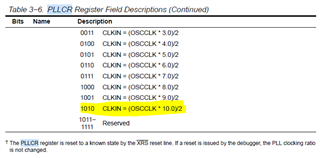

I am using TMS320F2812 DSP. Crystal 30MHZ, PLLCR=0x000A (i.e 5x), Clock 150MHZ, and XCLKOUT(pin-119) = 75MHZ.

But sometimes during power on condition, XCLKOUT showing only 15MHZ. i.e half of crystal value.

I am providing desired delay of 131072 cycles delay after writing to PLLCR register.

I am stuck at this problem. please explain role of XPLLDIS, XRS, TRST pins role on this problem.

please help me to resolve this.

Thanks alot,

Praveen Vemula.