Part Number: TMS320F28P550SJ

Tool/software:

Hi,

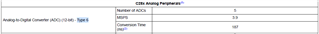

According to the data sheet ('Data sheet F28P55x'), it says the conversion time for each sample can be 180ns.

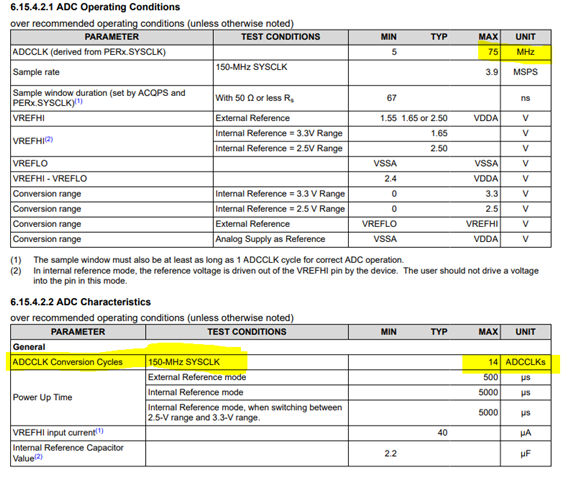

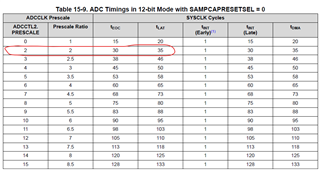

But if you look at the ADC specs from the user manual, I believe for F28P550SJ (150MHz sys clock rate), the ADC peripheral clock can only go as fast as 75MHz. That means we need to set Prescale = 2, which leads to the conversion time way longer than 180ns.

Can you please explain to me why 180ns conversion time was used in the Data Sheet?

Thank you,

Frank