Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

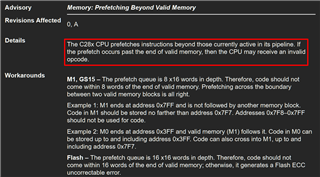

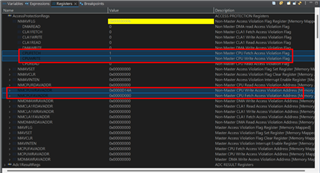

.cmd file for CPU2:RAMM0M1 : origin = 0x000002, length = 0x0007F6 /* on-chip RAM block M1 */RAMM1_RSVD : origin = 0x0007F8, length = 0x000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */RAMD0D1 : origin = 0x00C000, length = 0x001000// This section is set to owned by CPU1 for dataCPU1RAMGS0GS6 : origin = 0x00D000, length = 0x007000// This section is set to owned by CPU1 for RamfuncCPU1RAMGS7GS9 : origin = 0x014000, length = 0x003000// This section is set to owned by CPU2 for dataCPU2RAMGS10GS12 : origin = 0x017000, length = 0x003000// This section is set to owned by CPU2 for RamfuncCPU2RAMGS13GS15 : origin = 0x01A000, length = 0x003000 RAMD0D1 is immediately followed by CPU1RAMGS0GS6, which is allocated for CPU1's data, should the last 8 x 16 words of CPU2's RAMD0D1 block be reserved to avoid prefetching into an invalid memory area?Follow-up question: Based on the .cmd file above, what would happen if CPU2 prefetches into a memory region owned by CPU1? Are there any registers where this behavior can be observed?

Currently, we are encountering an issue where, when executing a function located at the very end of RAMD0D1 (occupying the last 8 words), there is a chance of jumping into illegal_isr(), but this does not always occur. We would like to confirm whether this behavior is caused by prefetching into an invalid memory region.