Tool/software:

Hello, engineers

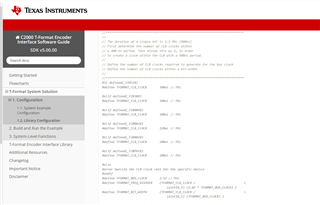

Now I plan to use CLB to implement the t-format protocol, look at the 28p55 datasheet, C2000Ware_MotorControl tformat_f28p65x_comms_demo, found very difficult to understand and use directly.

The documents in the following links are also invalid, I would like to get some help.

https://e2e.ti.com/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/1007238/faq-configurable-logic-block-clb---how-do-i-get-started

There are two other questions:

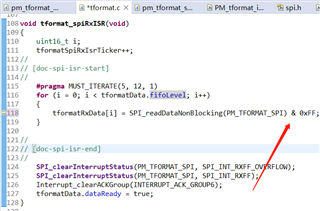

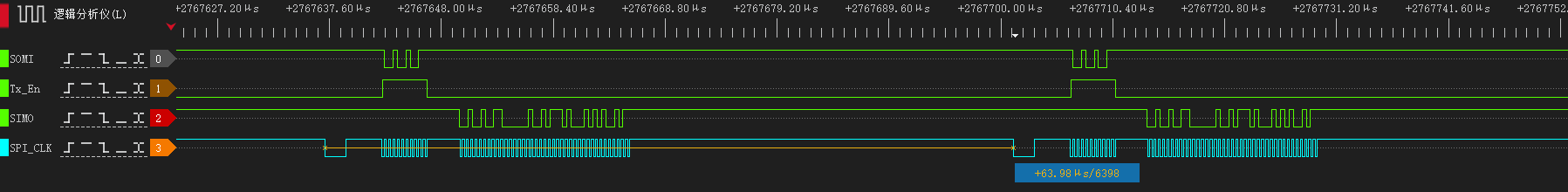

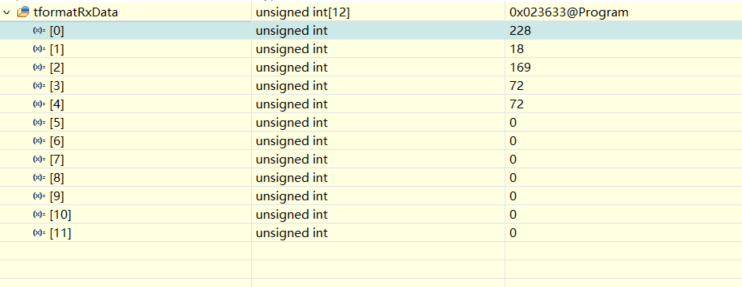

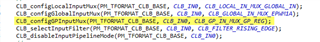

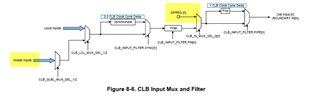

1. In the tformat_f28p65x_comms_demo routine, does CLB only control the direction of RS485? And after receiving the data returned by the encoder, is it first input to the CLB, and then the CLK that the CLB determines to the falling edge and then outputs the SPI?

2. There is no CLB library of 28p55 in the C2000Ware_MotorControl library, is the CLB library of 28p65 common to 28p55?