Other Parts Discussed in Thread: UNIFLASH, C2000WARE

Tool/software:

Hi,

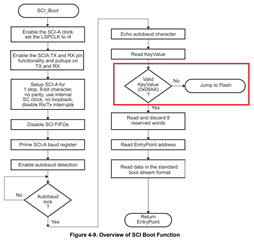

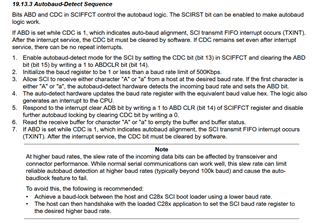

We have a requirement to flash the application using serial communication. To achieve this, we enabled SCI Boot Mode 1 since we are using SCI-A with GPIO pins 28 and 29.

Here are the steps we followed to enable SCI Boot Mode 1 and load the application:

- Set the OTP register Z1-BOOTCTRL (0x7801E) = 0x4955815A.

- Use the Serial Flash Programmer utility provided by TI.

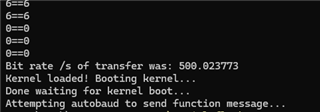

- The kernel and application were successfully flashed onto the board, and the system ran correctly. However, after a power cycle, the CPU goes into Hibernate Boot mode (refer to RTM: Figure 4-6, CPU1 Standalone and Hibernate Boot Flow).

Please help us configure the system to boot from flash so that the application runs correctly after the power cycle.

Regards,

Aditya