Part Number: TMS320F280039C

Tool/software:

- Previous thread

Dear TI expert,

I found the reason why I can't check SCI_RXSTATUS_BREAK flag in my code.

If I make SCI Break (keep SCI data line low over 82.5us), FE(Framing Error) and PE(Parity Error) bits(sometimes FE & OE & PE bits) are setted faster than BRKDT bit.

That's why DSSI_Break_Flag is not incresed in my code.

if((SCI_getRxStatus(SCIA_BASE) & SCI_RXSTATUS_BREAK)) // DSSI Break -> Configuration Phase

{

DSSI_Break_Flag++;

SCI_clearInterruptStatus(SCIA_BASE, SCI_INT_RXRDY_BRKDT);

SCI_performSoftwareReset(SCIA_BASE);

return;

}

else if((SCI_getRxStatus(SCIA_BASE) & (SCI_RXSTATUS_ERROR | SCI_RXSTATUS_PARITY | SCI_RXSTATUS_OVERRUN | SCI_RXSTATUS_FRAMING)))

{

SCI_performSoftwareReset(SCIA_BASE);

SCI_resetChannels(SCIA_BASE);

return;

}

Is it normal for the FE&PE&OE error to occur together if I make SCI Break?

If I want to use BRKDT error only in SCI Break, is there any method that I can avoid FE&PE&OE error?

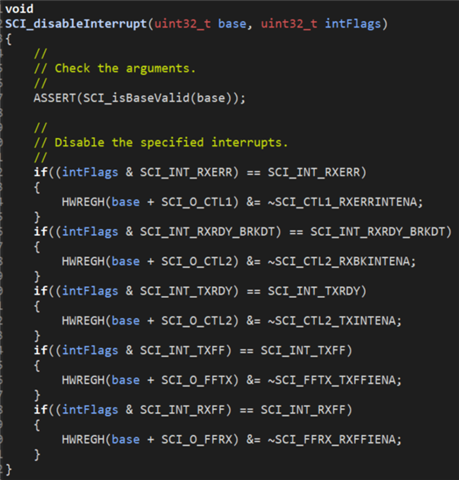

In TI library, there is no function that disable FE, PE and OE error.

Please check and advice,

Thanks.

Best Regards,

From. Jaehoon