Tool/software:

Dear Experts,

I am trying to copy the ADC_ISR code in the RAM from the flash for better speed. To perform this, I added "#define _FLASH" to the main() to include InitFlash() in InitSysCtrl();.

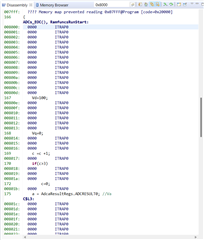

Then "#pragma CODE_SECTION(ADCs_EOC, "ramfuncs")" is added before the ADC_ISR. During thedebug I just checked if the ADC_ISR is loaded in the designated address as per the linker file and it was found expected, which you can see in the 1st image! it starts from 0x8000 which is strat address of LS0RAM. Once the RUN was pressed everything seemed perfect - acquiring analog signals and gneratin as per the analog signal and triggering ADC by the ePWM1.

#include "F28x_Project.h"

#include <math.h>

#include <stdio.h>

#define _FLASH

extern void InitSysCtrl(void);

extern void InitPieCtrl(void);

extern void InitPieVectTable(void);

#define TWO_PI 6.283185307179586476925286766559

interrupt void ADCs_EOC(void);

void Initialize_GPIO(void);

void Custom_Init(void);

void PWM1_Init(void);

void Init_ADCs(void);

void X_bar(void);

int buff[100],i,b,c,d=0;

float pi,V_alpha,V_beta,Vd,Vq,R,Y,B,temp,temp2,theta,a;

void main(void)

{

InitSysCtrl();

Custom_Init();

PWM1_Init();

Init_ADCs();

DINT;

Initialize_GPIO();

InitPieCtrl();

IER = 0x0000;

IFR = 0x0000;

InitPieCtrl();

InitPieVectTable();

EALLOW;

PieCtrlRegs.PIEIER1.bit.INTx1 = 1; //ADC-A1

PieVectTable.ADCA1_INT = &ADCs_EOC;

PieCtrlRegs.PIECTRL.bit.ENPIE= 1;

EDIS;

IER |= 1;

EINT; // Enable Global interrupt INTM

ERTM; // Enable Global realtime interrupt DBGM

while(1)

{

}

}

void Initialize_GPIO(void)

{

EALLOW;

//GPIO 18 - Xbar input

/* GpioCtrlRegs.GPAMUX2.bit.GPIO18 = 0;

// GpioCtrlRegs.GPAGMUX2.bit.GPIO18 = 0;

// GpioCtrlRegs.GPAPUD.bit.GPIO18 = 1;

// GpioCtrlRegs.GPADIR.bit.GPIO18 = 0;

// GpioCtrlRegs.GPACSEL3.bit.GPIO18 = 0;

// GpioCtrlRegs.GPAQSEL2.bit.GPIO18 = 3;

InputXbarRegs.INPUT5SELECT = 18;

*/

// LED out

GpioCtrlRegs.GPBDIR.bit.GPIO34 = 1;

GpioCtrlRegs.GPADIR.bit.GPIO31 = 1;

GpioCtrlRegs.GPCDIR.bit.GPIO73= 1;

//PWMs

GpioCtrlRegs.GPAMUX1.bit.GPIO0 = 1; //ePWM1A

GpioCtrlRegs.GPAMUX1.bit.GPIO2 = 1; //ePWM2A

GpioCtrlRegs.GPAMUX1.bit.GPIO4 = 1; //ePWM3A

GpioCtrlRegs.GPAMUX1.bit.GPIO6 = 1; //ePWM4A

GpioCtrlRegs.GPAMUX1.bit.GPIO8 = 1; //ePWM5A

GpioCtrlRegs.GPAMUX1.bit.GPIO10 = 1; //ePWM6A

EDIS;

}

void Custom_Init(void)

{

EALLOW;

ClkCfgRegs.CLKSRCCTL1.bit.OSCCLKSRCSEL=1;

ClkCfgRegs.AUXPLLMULT.bit.IMULT=20;

ClkCfgRegs.SYSCLKDIVSEL.bit.PLLSYSCLKDIV=0;

ClkCfgRegs.SYSPLLCTL1.bit.PLLCLKEN = 1;

ClkCfgRegs.LOSPCP.bit.LSPCLKDIV = 2;

ClkCfgRegs.PERCLKDIVSEL.bit.EPWMCLKDIV = 0;

CpuSysRegs.PCLKCR0.bit.CPUTIMER0 = 1;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 1; ///source initsysctrl

CpuSysRegs.PCLKCR2.bit.EPWM1 = 1;

CpuSysRegs.PCLKCR2.bit.EPWM2 = 1;

CpuSysRegs.PCLKCR2.bit.EPWM3 = 1;

CpuSysRegs.PCLKCR2.bit.EPWM4 = 1;

CpuSysRegs.PCLKCR2.bit.EPWM5 = 1;

CpuSysRegs.PCLKCR2.bit.EPWM6 = 1;

CpuSysRegs.PCLKCR2.bit.EPWM7 = 1;

CpuSysRegs.PCLKCR13.bit.ADC_A = 1;

CpuSysRegs.PCLKCR0.bit.CLA1 = 1;

DevCfgRegs.CPUSEL0.bit.EPWM1 = 0;

Flash0CtrlRegs.FPAC1.bit.PMPPWR = 1; // Enable flash pump

Flash0CtrlRegs.FRDCNTL.bit.RWAIT = 3; // Adjust wait states

EDIS;

}

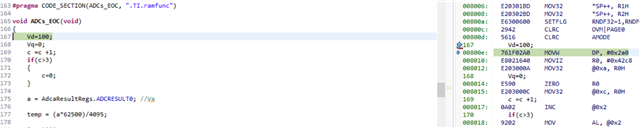

#pragma CODE_SECTION(ADCs_EOC, "ramfuncs")

void ADCs_EOC(void)

{

Vd=100;

Vq=0;

c =c +1;

if(c>3)

{

c=0;

}

a = AdcaResultRegs.ADCRESULT0; //Va

temp = (a*62500)/4095;

R = 1000-a;

EPwm1Regs.CMPA.bit.CMPA = temp;

EPwm1Regs.CMPB.bit.CMPB = temp + 9000;

i= i+1;

EPwm1Regs.ETCLR.bit.SOCA = 1;

AdcaRegs.ADCINTFLGCLR.bit.ADCINT1 = 1; //clear INT1 flag

PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;

}

void PWM1_Init(void)

{

EALLOW;

//R Phase

EPwm1Regs.TBCTL.bit.CTRMODE = 0; // Count up

EPwm1Regs.TBPRD = 62500; // Set timer period

EPwm1Regs.TBCTL.bit.PHSEN = 0; // 1 for external SYNC

EPwm1Regs.TBPHS.bit.TBPHS = 0x0000; // Phase is 0

EPwm1Regs.TBCTR = 0x0000; // Clear counter

EPwm1Regs.TBCTL.bit.HSPCLKDIV = 2; // Clock ratio to SYSCLKOUT

EPwm1Regs.TBCTL.bit.CLKDIV = 4;

EPwm1Regs.TBCTL.bit.SYNCOSEL = 1;

// Setup shadow register load on ZERO

EPwm1Regs.CMPCTL.bit.SHDWAMODE = 0;

EPwm1Regs.CMPCTL.bit.SHDWBMODE = 0;

EPwm1Regs.CMPCTL.bit.LOADAMODE = 0;

EPwm1Regs.CMPCTL.bit.LOADBMODE = 0;

// Set Compare values

// Set compare A value

// Set actions

EPwm1Regs.AQCTLA.all = 0;

EPwm1Regs.AQCTLA.bit.CAU = 2; // Set PWM1A on TBCTR = CMPA

EPwm1Regs.AQCTLA.bit.CBU = 1; // Clear PWM1A on TBCTR = CMPB= CMPA + 100

//SOCA to ADC

EPwm1Regs.ETSEL.bit.SOCAEN=1;

EPwm1Regs.ETSEL.bit.SOCASEL=1;

EPwm1Regs.ETPS.bit.SOCAPRD = 1;

EPwm1Regs.ETCLR.bit.SOCA = 1;

EDIS;

}

void Init_ADCs(void)

{

EALLOW;

AdcaRegs.ADCCTL1.bit.INTPULSEPOS = 1;

AdcbRegs.ADCCTL1.bit.INTPULSEPOS = 1;

AdccRegs.ADCCTL1.bit.INTPULSEPOS = 1;

AdcaRegs.ADCCTL1.bit.ADCPWDNZ = 1;

AdcbRegs.ADCCTL1.bit.ADCPWDNZ = 1;

AdccRegs.ADCCTL1.bit.ADCPWDNZ = 1;

// DELAY_US(1);

AdcaRegs.ADCCTL2.bit.PRESCALE = 6;

AdcbRegs.ADCCTL2.bit.PRESCALE = 6;

AdccRegs.ADCCTL2.bit.PRESCALE = 6;

AdcaRegs.ADCSOC0CTL.bit.CHSEL = 0; //SOC0 will convert pin A0

AdcaRegs.ADCSOC1CTL.bit.CHSEL = 1; //SOC1 will convert pin A1

AdcaRegs.ADCSOC2CTL.bit.CHSEL = 2; //SOC2 will convert pin A2

AdcaRegs.ADCSOC3CTL.bit.CHSEL = 3; //SOC3 will convert pin A3

AdcaRegs.ADCSOC4CTL.bit.CHSEL = 4; //SOC4 will convert pin A4

AdcaRegs.ADCSOC5CTL.bit.CHSEL = 5; //SOC5 will convert pin A5

AdcaRegs.ADCSOC0CTL.bit.ACQPS = 14; //sample window is 100 SYSCLK cycles

AdcaRegs.ADCSOC1CTL.bit.ACQPS = 14; //sample window is 100 SYSCLK cycles

AdcaRegs.ADCSOC2CTL.bit.ACQPS = 14; //sample window is 100 SYSCLK cycles

AdcaRegs.ADCSOC3CTL.bit.ACQPS = 14; //sample window is 100 SYSCLK cycles

AdcaRegs.ADCSOC4CTL.bit.ACQPS = 14; //sample window is 100 SYSCLK cycles

AdcaRegs.ADCSOC5CTL.bit.ACQPS = 14; //sample window is 100 SYSCLK cycles

AdcaRegs.ADCBURSTCTL.bit.BURSTEN = 1;

AdcaRegs.ADCBURSTCTL.bit.BURSTSIZE = 11;

AdcaRegs.ADCBURSTCTL.bit.BURSTTRIGSEL = 5;

//interrupt

AdcaRegs.ADCINTSEL1N2.bit.INT1SEL = 0; //end of SOC0 will set INT1 flag

AdcaRegs.ADCINTSEL1N2.bit.INT1E = 1; //enable INT1 flag

AdcaRegs.ADCINTFLGCLR.bit.ADCINT1 = 1; //make sure INT1 flag is cleared

AdcaRegs.ADCINTSEL1N2.bit.INT1SEL = 0;

AdcaRegs.ADCSOC1CTL.bit.TRIGSEL = 05;

EDIS;

}

The followinf image shows the ADCISR which starts from 0x8000.

Everything seems normal until the microcontroller is RESET! I expected that it'd continue to do the intended functions (ePWM, acquiring analog, pwm trigering ADC), but it stopped doing so and ended up with ILLEGAL_ISR!

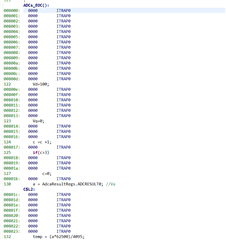

I suspected the memory and found the code is different to the previous view. I am not sure if this is culprit but just sharing the observations.

Please help me getting over this.

Regards,

Rajesh.