Other Parts Discussed in Thread: SYSCONFIG, C2000WARE

Tool/software:

Hello everyone, first time poster here.

I'm trying to set up the control of an H-bridge that will be controlled through fibre-optic cables ie logical signals.

GPIO 4 and GPIO 5 are turned high or low, and when this occurs, ePWM4 and ePWM5 are switched accordingly:

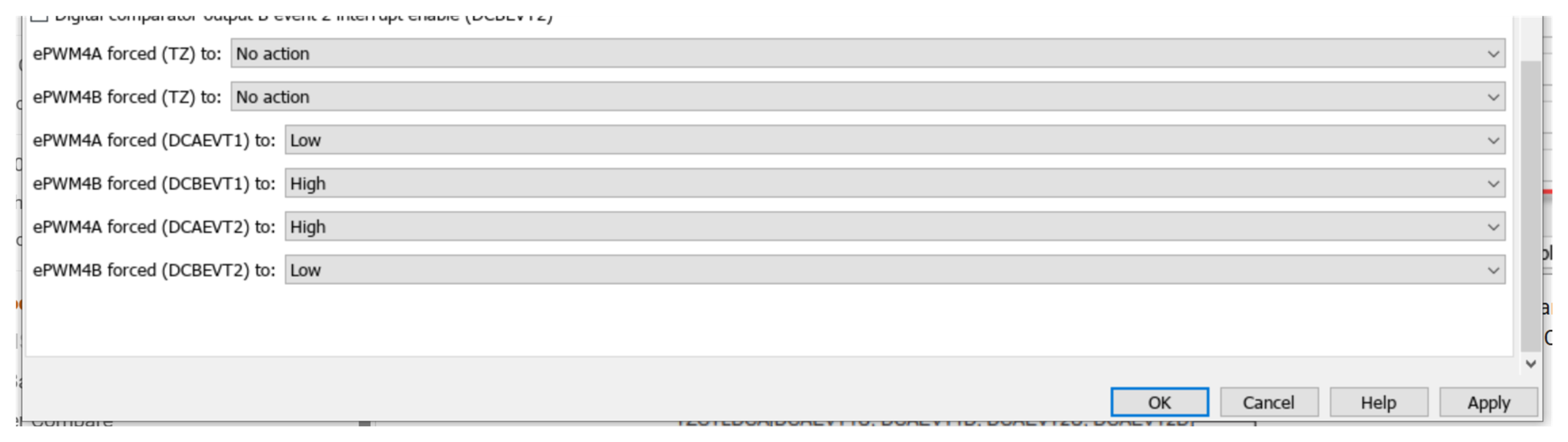

GPIO4 high:

ePWM4A=set

ePWM4B=clear

GPIO4 low:

ePWM4A=clear

ePWM4B=set

GPIO5 high/low:

ePWM5A=set/clear

ePWM5B=clear/set

I managed to implement this by routing the state of the gpios to TZ1 for ePWM4 and TZ2 for ePWM5 and using digital compare to switch the ePWM modules.

To the issue:

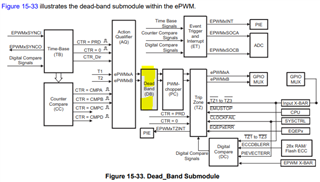

I need to implement a deadband to ensure ePWM4A &4B are not both high, as well as 5A and 5B to avoid possible short circuit.

I have been trying to use CLB in a similar way as Achieve Delayed Protection for Three-Level Inverter With CLB but as I am using the simulink-interface I have difficulty setting the counter. I also have difficulty setting up CLB for ePWM5 as it is not mirrored directly as a CLB tile and I need to use X-bar to route the signals to ePWM5 ( i think).

so to my question:

- Is this a reasonable approach?

- Any best case solutions on how to achieve the mirroring of GPIO-pins to control two ePWM modules (with added deadband) in the way i described above?

Any help appreciated, thanks!