Tool/software:

Hi experts,

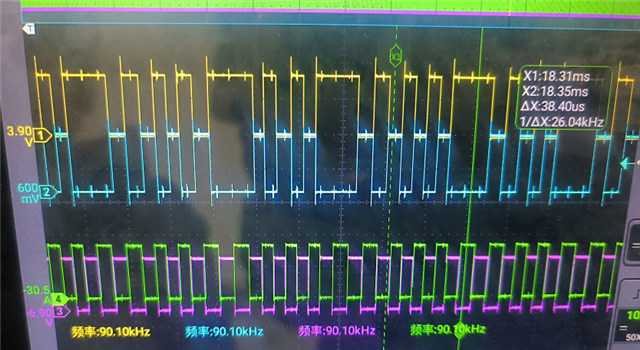

My client is developing Phase-shift & frequency changing function on EPWM1. And meet the issue of missing pulse. (yellow & blue: EPWM1AB; green & purple: EPWM2AB)

The EPWM1 have the same frequency with EPWM2. And EPWM1 receive the SYNC event from EPWM2 (when TBCTR = 0) to load the TBPRD from shadow to active. The EPWM1's TBPRD and CMPA are linking to EPWM2.

EPWM1 and EPWM2 are up-down counting mode. The AQ for them is CMPA-UP: DOWN and CMPA-DOWN: UP. Their duty is 50%. For EPWM2 there is no TBPHS only frequency changing, for EPWM1 there are both TBTHS and frequency changing.

When they changing the the frequency of EPWM from 90k to 70k directly, they will meet the missing pulse events on EPWM1.

We refer to this link: https://e2e.ti.com/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/1312604/tms320f28379d-tms320f28379d-phase-shift-pwm-missing-pulse and add the T1 event with AQ. It will reduce the number of missing pulse events but can not stop missing pulse event.

Are there any other suggestions for this issue?