Tool/software:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Does the information in this thread assist?

Regards,

Jason Osborn

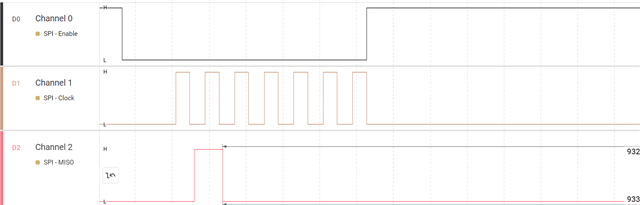

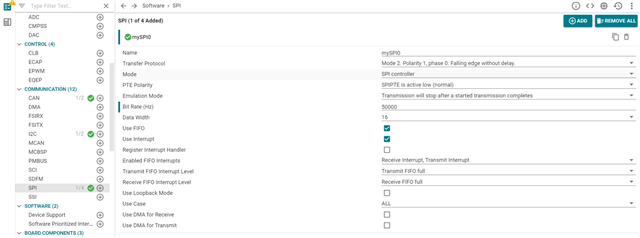

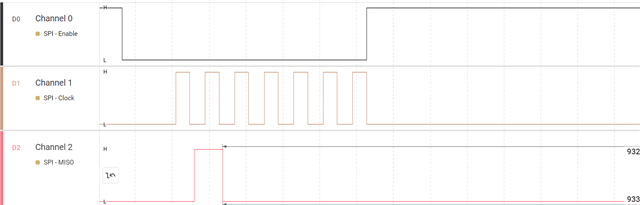

Hi Jason, I have referred this thread already and configured SPI for CPU2, but I am expecting 16 bit data signal with different clock, it is not getting reflected in analyzer tool, however same config settings are working in CPU1.

Apologies for the delay in response.

How is the data to be transferred being determined? If the SPI is configured correctly, then is it possible that there is an issue where CPU2 is not able to access the desired data?

Regards,

Jason Osborn

Hi Jason, I have created one array of uint16 data type in CPU2 itself, which has required data also checked by printing that variable in debug window on serial port it shows desired value is sent to SPI_writeDataNonBlocking function and for testing I have taken out all pins on Logic analyzer to check what is transmitted on SPI.

I have been looking and I don't think we have one explicitly in CPU2 for this device. I'll continue to look and try and find anything else which may be a problem. It's in the thread that I referenced, but just to double-check, have you used the GPIO_setMasterCore() function to assign the correct core to each of your SPI pins?

Regards,

Jason Osborn

Hi, Jason,

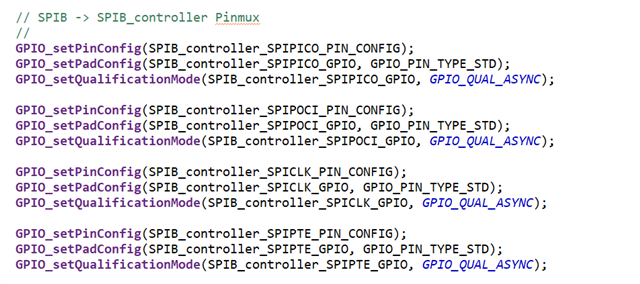

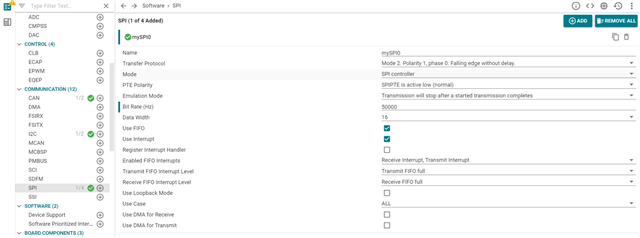

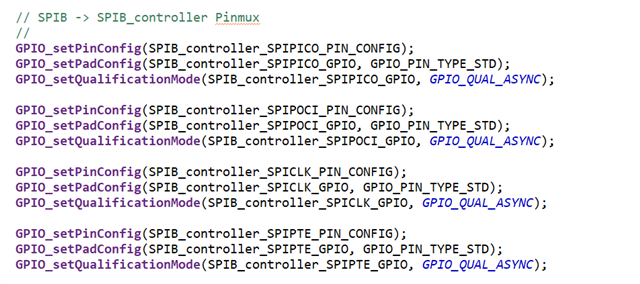

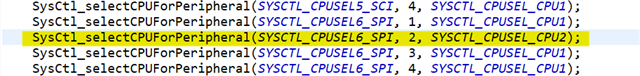

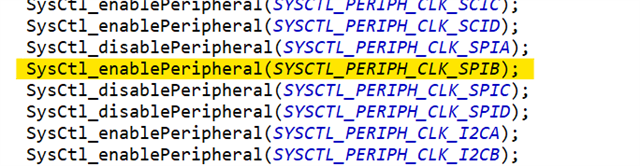

I have generated code using sys config tool, No I haven't directly used function GPIO_setMasterCore() but insted sys config generated SYSCTRL init function which will set SPI B core to CPU2 as shown in following snap.

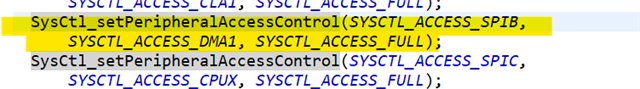

and also configured Full Access to SPIB channel and Selected clock in CPU1 sys config.

clock is selected as,

Do I need to manually configure instead of Sys Config?

can you share any SPI example code in CPU2 core.

I have been unable to find any CPU2 SPI examples, unfortunately.

Note that the GPIO and SysCtl functions are configuration functions for two different aspects of the MCU. I believe you may need both. Please add the GPIO configuration function in addition to what is already present.

Regards,

Jason Osborn