Tool/software:

This thread follows this one. We designed a custom board based on f28388d that uses the EMIF2 instead of EMIF1 to interface an SDRAM. We used the exact schematics from the F28379D_EMIF_DC reference design. Unfortunately this design doesn't seems not in production anymore, and we have not possibility to test it on a EMIF1 using LaunchPads. Furthermore, this design is announced to be compatible with the f28379d, not the f28388d. Most AN or related documents related to EMIF were released before the f28388d.

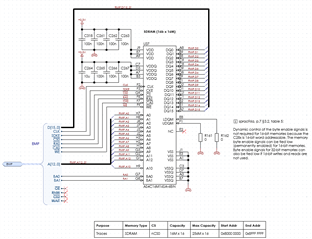

For the record, we uses this schematics:

The SDRAM was configured with the following code:

void configure_sdram(){

// Do not synchronize the EMIF2 pins

for (unsigned i = 53; i <= 68; i++){

GPIO_setPadConfig(i, GPIO_PIN_TYPE_PULLUP);

GPIO_setQualificationMode(i, GPIO_QUAL_ASYNC);

}

GPIO_setPinConfig(GPIO_68_EMIF2_D0);

GPIO_setPinConfig(GPIO_67_EMIF2_D1);

GPIO_setPinConfig(GPIO_66_EMIF2_D2);

GPIO_setPinConfig(GPIO_65_EMIF2_D3);

GPIO_setPinConfig(GPIO_64_EMIF2_D4);

GPIO_setPinConfig(GPIO_63_EMIF2_D5);

GPIO_setPinConfig(GPIO_62_EMIF2_D6);

GPIO_setPinConfig(GPIO_61_EMIF2_D7);

GPIO_setPinConfig(GPIO_60_EMIF2_D8);

GPIO_setPinConfig(GPIO_59_EMIF2_D9);

GPIO_setPinConfig(GPIO_58_EMIF2_D10);

GPIO_setPinConfig(GPIO_57_EMIF2_D11);

GPIO_setPinConfig(GPIO_56_EMIF2_D12);

GPIO_setPinConfig(GPIO_55_EMIF2_D13);

GPIO_setPinConfig(GPIO_54_EMIF2_D14);

GPIO_setPinConfig(GPIO_53_EMIF2_D15);

GPIO_setPinConfig(GPIO_98_EMIF2_A0);

GPIO_setPinConfig(GPIO_99_EMIF2_A1);

GPIO_setPinConfig(GPIO_100_EMIF2_A2);

GPIO_setPinConfig(GPIO_101_EMIF2_A3);

GPIO_setPinConfig(GPIO_102_EMIF2_A4);

GPIO_setPinConfig(GPIO_103_EMIF2_A5);

GPIO_setPinConfig(GPIO_104_EMIF2_A6);

GPIO_setPinConfig(GPIO_105_EMIF2_A7);

GPIO_setPinConfig(GPIO_106_EMIF2_A8);

GPIO_setPinConfig(GPIO_107_EMIF2_A9);

GPIO_setPinConfig(GPIO_108_EMIF2_A10);

GPIO_setPinConfig(GPIO_109_EMIF2_A11);

GPIO_setPinConfig(GPIO_95_EMIF2_A12);

GPIO_setPinConfig(GPIO_111_EMIF2_BA0);

GPIO_setPinConfig(GPIO_112_EMIF2_BA1);

GPIO_setPinConfig(GPIO_113_EMIF2_CAS);

GPIO_setPinConfig(GPIO_114_EMIF2_RAS);

GPIO_setPinConfig(GPIO_115_EMIF2_CS0N);

GPIO_setPinConfig(GPIO_117_EMIF2_SDCKE);

GPIO_setPinConfig(GPIO_118_EMIF2_CLK);

GPIO_setPinConfig(GPIO_120_EMIF2_WEN);

SysCtl_setEMIF2ClockDivider(SYSCTL_EMIF2CLK_DIV_2);

EMIF_setAccessProtection(EMIF2CONFIG_BASE, 0x0);

EMIF_commitAccessConfig(EMIF2CONFIG_BASE);

EMIF_lockAccessConfig(EMIF2CONFIG_BASE);

// Apply timing parameters

EMIF_SyncTimingParams syncTimingParams;

syncTimingParams.tRfc = 6; // Refresh to Active/Refresh command delay

syncTimingParams.tRp = 1; // Precharge to Activate delay

syncTimingParams.tRcd = 1; // Activate to Read/Write delay

syncTimingParams.tWr = 2; // Write recovery time

syncTimingParams.tRas = 4; // Active to Precharge delay

syncTimingParams.tRc = 6; // Active to Active/Auto Refresh delay

syncTimingParams.tRrd = 1; // Activate to Activate delay (different banks)

EMIF_setSyncTimingParams(EMIF2_BASE, &syncTimingParams);

EMIF_setSyncSelfRefreshExitTmng(EMIF2_BASE, 0x6U);

EMIF_setSyncRefreshRate(EMIF2_BASE, 781);

EMIF_SyncConfig syncConfig;

syncConfig.casLatency = EMIF_SYNC_CAS_LAT_3;

syncConfig.iBank = EMIF_SYNC_BANK_4;

syncConfig.narrowMode = EMIF_SYNC_NARROW_MODE_TRUE;

syncConfig.pageSize = EMIF_SYNC_COLUMN_WIDTH_9;

EMIF_setSyncMemoryConfig(EMIF2_BASE, &syncConfig);

}

To test the SDRAM, we used this snippet:

void test_sdram(){

for (uint32_t k = 0, i = 0; k < MEM_BUFFER_SIZE; k += 1, i += 5) {

extSDRAMBuf[k] = i;

}

for (uint32_t k = 0, i = 0; k < MEM_BUFFER_SIZE; k += 1, i += 5){

if (extSDRAMBuf[k] != i) {

testPass = false;

return;

}

testPass = true;

}

}

0, 5, 10 , 15

5, 5, 15, 15

- If we use memcpy_fast_far to read data from SDRAM into a local buffer, the values are correct.

- If we use memcpy_fast_far to write data to SDRAM, the values are still inconsistent, regardless of whether the buffer is 16, or 32 bits wide.

Therefore, our questions are:

- Is this a known limitation or behavior of the EMIF2 interface when accessing SDRAM with 16-bit buffers?

- Is there something wrong or missing in our configuration for 16-bit access?

- Why does reading with memcpy_fast_far work, but writing it does not?