Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hello,

An expert in this forum helped me for the watchdog. I still have a problem when managing the RAM configuration (FLASH is OK)

I join an archive of this simple project; based on TI example. If someone can take a look on it, I will appreciate.

Down here my problem:

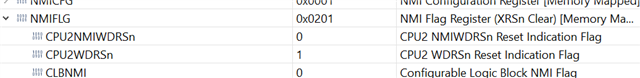

I configured a watchdog for the CPU1: it generates an interrupt, and a reset is asked in its ISR. The main while loop for this CPU executes only a simpel task (led blinking and scalar product), and a call to a "freezing" function. This finction makes the program enter in a infinite loop if the global variable uint16_freeze is set.

I want to test this:

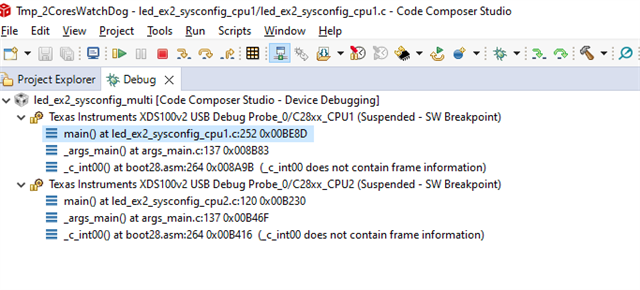

1) I open a debug session

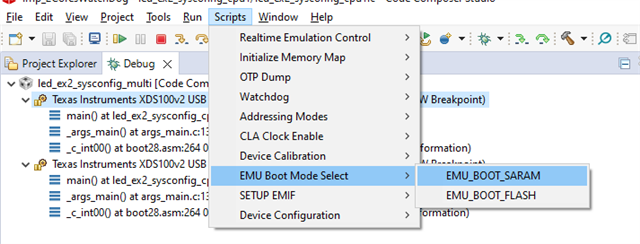

2) I select the right EMU mode for each project:

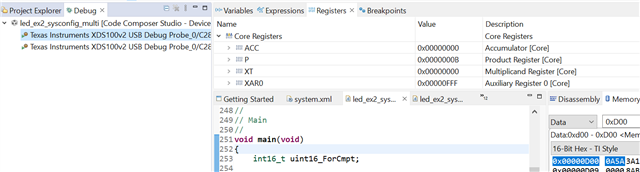

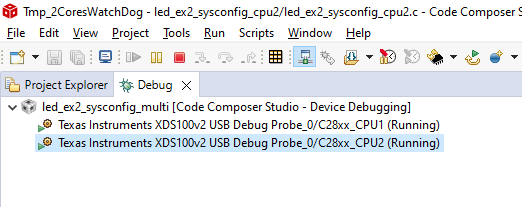

3) I launch the two projects

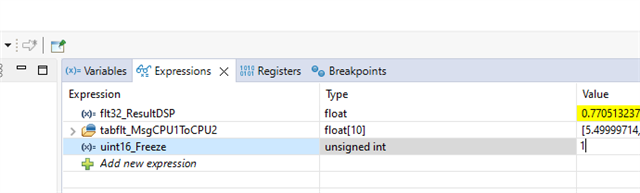

3- I force the freezing of the programm

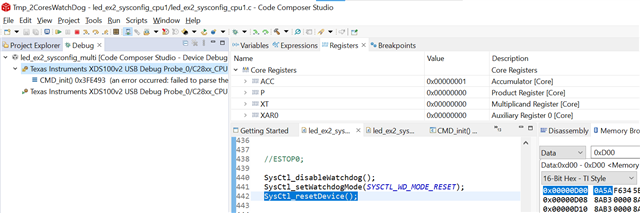

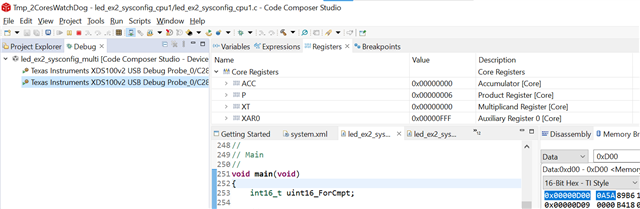

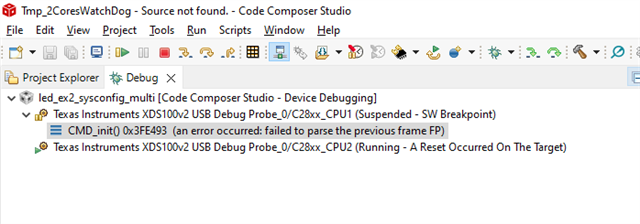

=> The CPU1 is halted because of an error:

Can somebody tell me what I did wrong ?

thank you