Tool/software:

Hi

I need to design a custom bootloader, which i am planning to flash to Bank 0

Applcation firmware i am planning to flash to Bank1 and Bank2, since the size may exceed 256KB

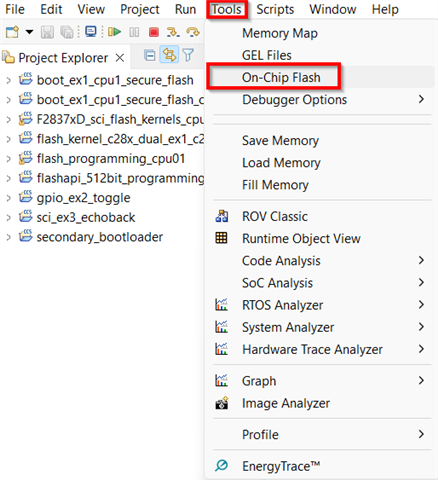

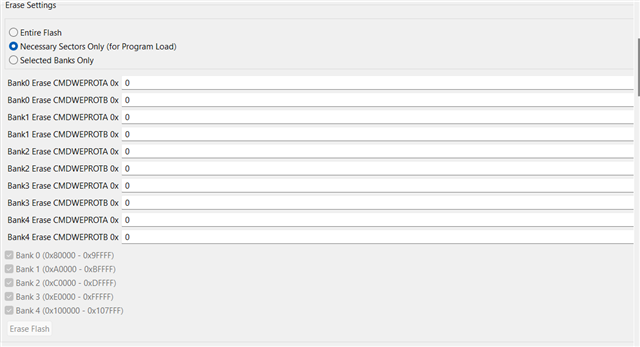

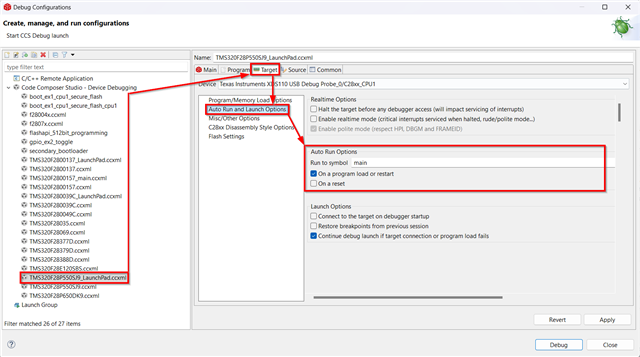

Now i have created cmd for both code and done flash erase settings correctly in ccs and flashed both.

I am building both application and bootloader with CPU1_FLASH

cmd for application

MEMORY

{

//BEGIN : origin = 0x0C0000, length = 0x000002 // <-- Updated codestart to BANK2

BOOT_RSVD : origin = 0x000002, length = 0x0001AF

RAMM0 : origin = 0x0001B1, length = 0x00024F

RAMM1 : origin = 0x000400, length = 0x000400

RAMD0 : origin = 0x00C000, length = 0x002000

RAMD1 : origin = 0x00E000, length = 0x002000

RAMD2 : origin = 0x01A000, length = 0x002000

RAMD3 : origin = 0x01C000, length = 0x002000

RAMD4 : origin = 0x01E000, length = 0x002000

RAMD5 : origin = 0x020000, length = 0x002000

RAMLS0 : origin = 0x008000, length = 0x000800

RAMLS1 : origin = 0x008800, length = 0x000800

RAMLS2 : origin = 0x009000, length = 0x000800

RAMLS3 : origin = 0x009800, length = 0x000800

RAMLS4 : origin = 0x00A000, length = 0x000800

RAMLS5 : origin = 0x00A800, length = 0x000800

RAMLS6 : origin = 0x00B000, length = 0x000800

RAMLS7 : origin = 0x00B800, length = 0x000800

RAMLS8 : origin = 0x022000, length = 0x002000

RAMLS9 : origin = 0x024000, length = 0x002000

RAMGS0 : origin = 0x010000, length = 0x002000

RAMGS1 : origin = 0x012000, length = 0x002000

RAMGS2 : origin = 0x014000, length = 0x002000

RAMGS3 : origin = 0x016000, length = 0x002000

RAMGS4 : origin = 0x018000, length = 0x002000

/* Flash Banks */

FLASH_BANK0 : origin = 0x080000, length = 0x20000

FLASH_BANK1 : origin = 0x0A0000, length = 0x20000

FLASH_BANK2 : origin = 0x0C0000, length = 0x20000

FLASH_BANK3 : origin = 0x0E0000, length = 0x20000 // <-- Uncommented

CPU1TOCPU2RAM : origin = 0x03A000, length = 0x000400

CPU2TOCPU1RAM : origin = 0x03B000, length = 0x000400

CLATOCPURAM : origin = 0x001480, length = 0x000080

CPUTOCLARAM : origin = 0x001500, length = 0x000080

CLATODMARAM : origin = 0x001680, length = 0x000080

DMATOCLARAM : origin = 0x001700, length = 0x000080

CANA_MSG_RAM : origin = 0x049000, length = 0x000800

CANB_MSG_RAM : origin = 0x04B000, length = 0x000800

RESET : origin = 0x3FFFC0, length = 0x000002

}

SECTIONS

{

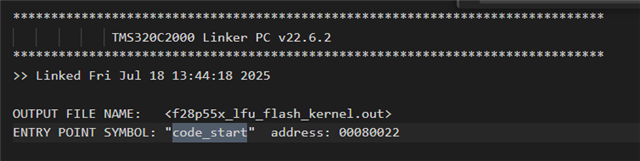

codestart : > FLASH_BANK1 // <-- uses BANK1 address (0x0A0000)

.app_entry : > 0x0A0000

.text : >> FLASH_BANK1 | FLASH_BANK2, ALIGN(8) // <-- modified from BANK0/BANK1

.cinit : > FLASH_BANK1, ALIGN(8)

.switch : > FLASH_BANK1, ALIGN(8)

.reset : > RESET, TYPE = DSECT

.ramfuncs : LOAD = FLASH_BANK1,

RUN = RAMLS0,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_END(_RamfuncsRunEnd),

PAGE = 0

.stack : > RAMM1

#if defined(__TI_EABI__)

.bss : >> RAMD0 | RAMD1 | RAMD2 | RAMD3

.freertosStaticStack : > RAMD1, type=NOINIT

.bss:output : > RAMLS3

.init_array : > FLASH_BANK1, ALIGN(8)

.const : > FLASH_BANK1, ALIGN(8)

.data : > RAMLS5

.sysmem : > RAMGS0

#else

.pinit : > FLASH_BANK1, ALIGN(8)

.ebss : >> RAMLS5 | RAMLS6

.econst : > FLASH_BANK1, ALIGN(8)

.esysmem : > RAMLS5

#endif

ramgs0 : > RAMGS0, type=NOINIT

ramgs1 : > RAMGS1, type=NOINIT

ramgs2 : > RAMGS2, type=NOINIT

MSGRAM_CPU1_TO_CPU2 > CPU1TOCPU2RAM, type=NOINIT

MSGRAM_CPU2_TO_CPU1 > CPU2TOCPU1RAM, type=NOINIT

#if defined(__TI_EABI__)

.TI.ramfunc : {} LOAD = FLASH_BANK1,

RUN = RAMLS0,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

#else

.TI.ramfunc : {} LOAD = FLASH_BANK1,

RUN = RAMLS0,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

ALIGN(8)

#endif

}

/*

//===========================================================================

// End of file.

//===========================================================================

cmd for bootloader

MEMORY

{

//BEGIN : origin = 0x080000, length = 0x000002 // Update the codestart location as needed

BOOT_RSVD : origin = 0x000002, length = 0x0001AF /* Part of M0, BOOT rom will use this for stack */

RAMM0 : origin = 0x0001B1, length = 0x00024F

RAMM1 : origin = 0x000400, length = 0x000400

RAMD0 : origin = 0x00C000, length = 0x002000

RAMD1 : origin = 0x00E000, length = 0x002000

RAMD2 : origin = 0x01A000, length = 0x002000 // Can be mapped to either CPU1 or CPU2. When configured to CPU2, use the address 0x8000. User should comment/uncomment based on core selection

RAMD3 : origin = 0x01C000, length = 0x002000 // Can be mapped to either CPU1 or CPU2. When configured to CPU2, use the address 0xA000. User should comment/uncomment based on core selection

RAMD4 : origin = 0x01E000, length = 0x002000 // Can be mapped to either CPU1 or CPU2. When configured to CPU2, use the address 0xC000. User should comment/uncomment based on core selection

RAMD5 : origin = 0x020000, length = 0x002000 // Can be mapped to either CPU1 or CPU2. When configured to CPU2, use the address 0xE000. User should comment/uncomment based on core selection

RAMLS0 : origin = 0x008000, length = 0x000800

RAMLS1 : origin = 0x008800, length = 0x000800

RAMLS2 : origin = 0x009000, length = 0x000800

RAMLS3 : origin = 0x009800, length = 0x000800

RAMLS4 : origin = 0x00A000, length = 0x000800

RAMLS5 : origin = 0x00A800, length = 0x000800

RAMLS6 : origin = 0x00B000, length = 0x000800

RAMLS7 : origin = 0x00B800, length = 0x000800

RAMLS8 : origin = 0x022000, length = 0x002000 // When configured as CLA program use the address 0x4000

RAMLS9 : origin = 0x024000, length = 0x002000 // When configured as CLA program use the address 0x6000

// RAMLS8_CLA : origin = 0x004000, length = 0x002000 // Use only if configured as CLA program memory

// RAMLS9_CLA : origin = 0x006000, length = 0x002000 // Use only if configured as CLA program memory

RAMGS0 : origin = 0x010000, length = 0x002000

RAMGS1 : origin = 0x012000, length = 0x002000

RAMGS2 : origin = 0x014000, length = 0x002000

RAMGS3 : origin = 0x016000, length = 0x002000

RAMGS4 : origin = 0x018000, length = 0x002000

/* Flash Banks (128 sectors each) */

FLASH_BANK0 : origin = 0x080000, length = 0x20000 // Can be mapped to either CPU1 or CPU2. User should comment/uncomment based on core selection

FLASH_BANK1 : origin = 0x0A0000, length = 0x20000 // Can be mapped to either CPU1 or CPU2. User should comment/uncomment based on core selection

FLASH_BANK2 : origin = 0x0C0000, length = 0x20000 // Can be mapped to either CPU1 or CPU2. User should comment/uncomment based on core selection

FLASH_BANK3 : origin = 0x0E0000, length = 0x20000 // Can be mapped to either CPU1 or CPU2. User should comment/uncomment based on core selection

// FLASH_BANK4 : origin = 0x100000, length = 0x20000 // Can be mapped to either CPU1 or CPU2. User should comment/uncomment based on core selection

CPU1TOCPU2RAM : origin = 0x03A000, length = 0x000400

CPU2TOCPU1RAM : origin = 0x03B000, length = 0x000400

CLATOCPURAM : origin = 0x001480, length = 0x000080

CPUTOCLARAM : origin = 0x001500, length = 0x000080

CLATODMARAM : origin = 0x001680, length = 0x000080

DMATOCLARAM : origin = 0x001700, length = 0x000080

CANA_MSG_RAM : origin = 0x049000, length = 0x000800

CANB_MSG_RAM : origin = 0x04B000, length = 0x000800

RESET : origin = 0x3FFFC0, length = 0x000002

}

SECTIONS

{

codestart : > FLASH_BANK0

.text : > FLASH_BANK0, ALIGN(8)

.cinit : > FLASH_BANK0, ALIGN(8)

.switch : > FLASH_BANK0, ALIGN(8)

.reset : > RESET, TYPE = DSECT /* not used, */

.stack : > RAMM1

#if defined(__TI_EABI__)

.bss : > RAMLS5

.bss:output : > RAMLS3

.init_array : > FLASH_BANK0, ALIGN(8)

.const : > FLASH_BANK0, ALIGN(8)

.data : > RAMLS5

.sysmem : > RAMLS4

#else

.pinit : > FLASH_BANK0, ALIGN(8)

.ebss : >> RAMLS5 | RAMLS6

.econst : > FLASH_BANK0, ALIGN(8)

.esysmem : > RAMLS5

#endif

ramgs0 : > RAMGS0, type=NOINIT

ramgs1 : > RAMGS1, type=NOINIT

ramgs2 : > RAMGS2, type=NOINIT

MSGRAM_CPU1_TO_CPU2 > CPU1TOCPU2RAM, type=NOINIT

MSGRAM_CPU2_TO_CPU1 > CPU2TOCPU1RAM, type=NOINIT

#if defined(__TI_EABI__)

.TI.ramfunc : {} LOAD = FLASH_BANK0,

RUN = RAMLS0,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

#else

.TI.ramfunc : {} LOAD = FLASH_BANK0,

RUN = RAMLS0,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

ALIGN(8)

#endif

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

Jump application in BL

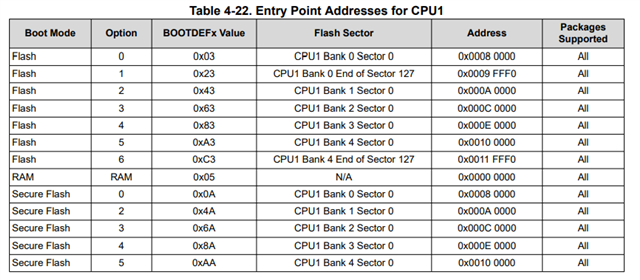

#define APP_ENTRY_ADDRESS 0x0A0000 // Must match app linker section

typedef void (*app_entry_t)(void);

void jumpToApp(void)

{

DINT;

EALLOW;

SysCtl_disableWatchdog();

// Optional: clear PIE, IER, IFR

IER = 0x0000;

IFR = 0x0000;

EDIS;

app_entry_t app = (app_entry_t)(APP_ENTRY_ADDRESS);

if ((uint32_t)app != 0xFFFFFFFF && (uint32_t)app != 0x00000000)

{

SYSTEM_LOG_UART(LOG, __func__, "Jumping to Application at 0x%08lx", (uint32_t)app);

;

app(); // Call the application entry function

}

else

{

SYSTEM_LOG_UART(LOG, __func__, "Invalid App Entry, fallback or halt");

asm(" ESTOP0");

}

}result i am getting:-

If flash application , it is booting from application

If flash bootloader , its bootng from boot loader but not jumping to application

What i am expecting

1. My Bootloader should flash to Bank0 from CCS without disturbing any other banks

2.My Application should flash to Bank1 &2 from CCS without disturbing any other banks

3. Application should not boot by its own

4. Always the board boot from Bootloader & it should boot the pplication from Bank1

Please let me know the change need in cmd & bootloader